Over the recent years, the volume and velocity of discussions relating to chiplets have intensified. A major reason for this is the projected market opportunity. According to research firm Omdia, chiplets driven market is expected to be $6B by 2024 from just $645M in 2018. That’s an impressive nine-fold projected increase over… Read More

Tag: 3nm

Is IBM’s 2nm Announcement Actually a 2nm Node?

IBM has announced the development of a 2nm process.

IBM Announcement

What was announced:

- “2nm”

- 50 billion transistors in a “thumbnail” sized area later disclosed to be 150mm2 = 333 million transistors per millimeter (MTx/mm2).

- 44nm Contacted Poly Pitch (CPP) with 12nm gate length.

- Gate All Around (GAA), there are several ways

How to Spend $100 Billion Dollars in Three Years

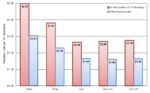

TSMC recently announced plans to spend $100 billion dollars over three years on capital. For 2021 they announced $30B in total capital with 80% on advanced nodes (7nm and smaller), 10% on packaging and masks and 10% on “specialty”.

If we take a guess at the capital for each year, we can project something like $30B for 2021 (announced),… Read More

Intel’s IDM 2.0

In January I presented at the ISS conference a comparison of Intel’s, Samsung’s and TSMC’s leading edge offerings. You can read a write-up of my presentation here.

With the problems going on at Intel, that article generated a lot of interest in the investment community, and I have been holding a lot of calls with analysts who are trying… Read More

SPIE 2021 – ASML DUV and EUV Updates

At the SPIE Advanced Lithography Conference held in February, ASML presented the latest information on their Deep Ultraviolet (DUV) and Extreme Ultraviolet (EUV) exposure systems. I recently got to interview Mike Lercel of ASML to discuss the presentations.

DUV

Despite all the attention EUV is getting, most layers are still… Read More

TSMC Plans Six Wafer Fabs in Arizona

There are reports in the media that TSMC is now planning six Fabs in Arizona (the image above is Fab 18 in Taiwan). The original post I saw referred to a Megafab and claimed six fabs with 100,000 wafers per month of capacity (wpm) for $35 billion dollars. The report further claimed it would be larger than TSMC fabs in Taiwan.

This report… Read More

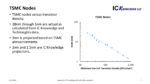

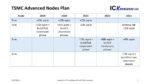

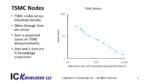

Intel Node Names

There is a lot of interest right now in how Intel compares to the leading foundries and what the future may hold.

Several years ago, I published several extremely popular articles converting processes from various companies to “Equivalent Nodes” (EN). Nodes were at one time based on actual physical features of processes but had… Read More

ISS 2021 – Scotten W. Jones – Logic Leadership in the PPAC era

I was asked to give a talk at the 2021 ISS conference and the following is a write up of the talk.

The title of the talk is “Logic Leadership in the PPAC era”.

The talk is broken up into three main sections:

- Background information explaining PPAC and Standard Cells.

- A node-by-node comparisons of companies running leading edge logic

IEDM 2020 Starts this Weekend

As I have discussed before, I believe that IEDM is the premier technical conference for understanding leading edge process technologies. Beginning this coming weekend, this year’s edition of IEDM will be held virtually, and I highly recommend attending.

The conference held a press briefing last Monday. The tutorial and short… Read More

No Intel and Samsung are not passing TSMC

Seeking Alpha just published an article about Intel and Samsung passing TSMC for process leadership. The Intel part seems to be a theme with them, they have talked in the past about how Intel does bigger density improvements with each generation than the foundries but forget that the foundries are doing 5 nodes in the time it takes… Read More