As Moore’s law started saturating on a single semiconductor die, the semiconductor community came up with the approach of growing vertically by stacking dies one above other in a 3D-IC arrangement. However, a major concern with a 3D-IC is that the heat generated by each die can get trapped in the stack, and hence it’s extremely important… Read More

Tag: 3d-ic

GSA 3DIC

At the GSA Silicon Summit this afternoon there was a discussion of 3D IC and 2.5D IC. The session was moderated by Javier DeLaCruz of eSilicon and the panelists were:

- Calvin Cheung of ASE (an OSAT)

- Gil Lvey of OptimalTest (a test house)

- Bob Patti of Tezzaron (semiconductor company specializing in TSV-based designs)

- Riko Radojcic

How to meet 3Ps in 3D-ICs with sub-20nm Dies?

It feels to be at the top of semiconductor technology by having dies with high density of semiconductor design at sub-20nm technology node stacked together into a 3D-IC to form a complete SoC which can accommodate billions of gates. However there are multiple factors to be looked at in order to make that successful amid often conflicting… Read More

Smart Strategies for Efficient Testing of 3D-ICs

3D-IC has a stack of dies connected and packaged together, and therefore needs new testing strategies other than testing a single die. It’s given that a single defective die can render the whole of 3D-IC unusable, so each die in the stack must be completely and perfectly tested before its entry into that stack. Looking at it from a … Read More

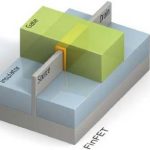

Designing an SoC with 16nm FinFET

IC designers contemplating the transition to 16nm FinFET technology for their next SoC need to be informed about design flow and IP changes, so TSMC teamed up with Cadence Design Systems today to present a webinar on that topic. I attended the webinar and will summarize my findings.

Shown below is a 3D layout concept of an ideal FinFET… Read More

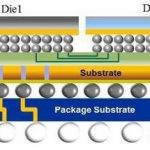

TSMC projects $800 Million of 2.5/3D-IC Revenues for 2016

At TSMC’s latest earnings call held mid January 2014, an analyst asked TSMC for a revenue forecast for their emerging 2.5/3D product line. C.C. Wei, President and Co-CEO answered: “800 Million Dollars in 2016 ”. TSMC has demonstrated great vision many times before. For me, an enthusiastic supporter of this technology, this statement… Read More

What will drive MEMS to drive I-o-T and I-o-P?

By I-o-P, I mean Internet-of-People- I couldn’t think of anything better than this to describe a technology which becomes your custodian for everything you do; you may consider it as your good companion through life or an invariably controlling spy. This is obvious with the embedded sensor techno-products such as Kolibree, a … Read More

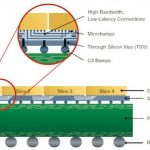

TSMC: 3D, 450mm, CoWoS and More

The first keynote at the Burlingame 3D conference was by Doug Yu of TSMC. Not surprisingly he was talking about 3D. In particular, TSMC has WLSI technology that they call CoWoS, which stands for chip-on-wafer-on-substrate which pretty much describes how it is built. This is the technology that Xilinx uses for its recently announced… Read More

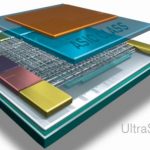

Xilinx Pulls Back the 20nm UltraScale Curtain

This week Xilinx has announced that “The Xilinx 20nm All Programmable UltraScale™ portfolio is now available with detailed device tables, product documentation, design tools and methodology support.”

Do you know what 20nm is? It’s small, tiny. Think about it this way, as I just learned today that one nanometer is about as long… Read More

Xilinx and TSMC: Volume Production of 3D Parts

A couple of weeks ago, Xilinx and TSMC announced the production release of the Virtex-7 HT family, the industry’s first heterogeneous 3D ICs in production. With this milestone, all Xilinx 28nm 3D IC families are now in volume production. These 28nm devices were developed on TSMC’s Chip-on-Wafer-on-Substrate (CoWoS)… Read More