Standard cell and memory IP are key enablers for new process node availability. These two items must be in place early and be completely ready for a process node to scale to volume. Development of both leaves no room for error and they require the highest performance possible. Foundries are extremely focused on this and spend a lot… Read More

Tag: 16ff+

How HBM Will Change SOC Design

High Bandwidth Memory (HBM) promises to do for electronic product design what high-rise buildings did for cities. Up until now, electronic circuits have suffered from the equivalent of suburban sprawl. HBM is a radical transformation of memory architecture that will have huge ripple effects on how SOC based electronics are … Read More

Xilinx Skips 10nm

At TSMC’s OIP Symposium recently, Xilinx announced that they would not be building products at the 10nm node. I say “announced” since I was hearing it for the first time, but maybe I just missed it before. Xilinx would go straight from the 16FF+ arrays that they have announced but not started shipping, and to the… Read More

Why Sidense OTP is Like the Armored Car of NVM

I have written about Sidense before, but last week at the TSMC Open Innovation Platform Forum, I had a chance to hear a talk by, and have lunch with Betina Hold Director of R&D at Sidense. Here is what I learned.

Sidense has been focusing on the growing market in what they like to call the smart connected universe. It is best to think… Read More

TSMC (Apple) Update Q2 2015!

The TSMC quarterly conference call was last week and of course it stirred up quite a bit of controversy. Let me share with you my experience, observations, and opinions and maybe together we can come up with an accurate prediction for 2016. First let’s take a look at 20nm and what people now call the “Apple effect.”

Correct… Read More

Xilinx Datacenter on a Chip

I talked recently about the Intel acquisition of Altera which seems to be all about using FPGA technology to build custom accelerators for the datacenter. Some algorithms, especially in search, vision, video and so on map much better onto a hardware fabric than being implemented in code on a regular microprocessor.

So if the heart… Read More

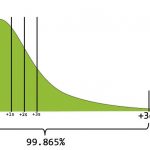

Antifuse is the New Foundation of NVM Below 16nm

Today the non-volatile memory (NVM) foundation is the eFuse. It is typically available for free from the foundry and is the default choice because, like Mount Everest, it is there. However, like Mount Everest it is big. It is also power hungry and slow. eFuse solutions blow the silicide on the poly line creating a change in resistance.… Read More

TSMC Processes Galore

Today was TSMC’s 2015 North American Technology Symposium. They talked about a lot of things but perhaps the most important was that they gave a lot of details of new processes, new fabs, and volume ramps.… Read More

TSMC’s OIP: Everything You Need for 16FF+ SoCs

Doing a modern SoC design is all about assembling IP and adding a small amount of unique IC design for differentiation (plus, usually, lots of software). If you re designing in a mature process then there is not a lot of difficulty finding IP for almost anything. But if you are designing in a process that has not yet reached high-volume… Read More

ANSYS Updates RedHawk for FinFET Nodes

Most designers are not using FinFETs yet, however the increased transistor density and power advantages they offer are compelling. Smaller feature sizes have been a consistent driver in semiconductor technology. Eventually the market will move more and more to FinFET processes, increasingly leaving behind planar transistors.… Read More