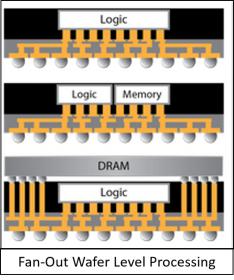

I caught up with John Ferguson of Mentor Graphics this week to learn more about a recent announcement that TSMC has extended its collaboration with Mentor in the area of Fan-Out Wafer Level Processing (FOWLP).

I caught up with John Ferguson of Mentor Graphics this week to learn more about a recent announcement that TSMC has extended its collaboration with Mentor in the area of Fan-Out Wafer Level Processing (FOWLP).

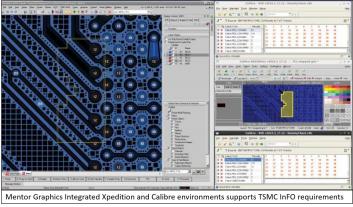

In March of last year Mentor and TSMC announced that they were collaborating on a design and verification flow for TSMC’s InFO (integrated Fan-Out) packaging technology using Mentor’s Xpedition Enterprise and Calibre nmDRC/RVE platforms. That flow allowed designers to layout the InFO structures with Mentor’s Xpedition Package Integrator and then use Calibre nmDRC for design rule checking with cross probing back into Xpedition using Calibre RVE.

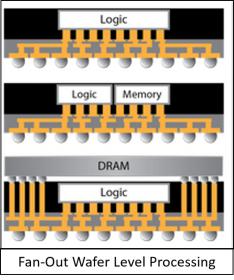

Since then, the Mentor and TSMC teams have been working closely together to enhance the flow to shorten design cycle times, minimize designer effort and ensure higher quality GDS hand-offs to improve first-time success rates. Key to the collaboration were efforts to ensure seamless assimilation of TSMC’s newest technologies whether it be single or multiple die on InFO packaging, with or without a substrate, and with or without package-on-package. To achieve this, Mentor has attacked several different areas.

Firstly, Mentor developed new Xpedition Enterprise functionality to make it easier to create InFO-specific fab-ready metal structures such as seal rings, parameterized mesh pad generation, degassing holes and additional metal for balancing metal density.

Mentor next added HyperLynx DRC technology to the flow for in-design InFO-specific manufacturing verification checks. HyperLynx DRC allows designers to find and fix DRC issues while still in the design phase reducing the number of iterations out to GDSII for DRC checking in Calibre. Final sign-off rule checking is still done with Calibre nmDRC for both die and InFO package design rule checks.

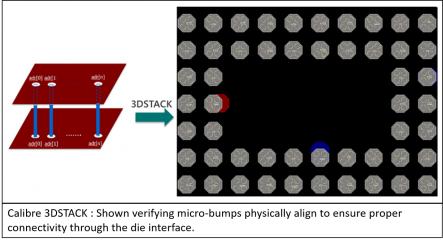

New to the flow with this release is the addition of Calibre 3DSTACK and the capability to do sign-off level layout-vs-schematic (LVS) checks for inter-die connectivity verification of the entire InFO-based package.

For IC designers this may sound trivial, but when you realize that you are possibly dealing with multiple die, each with their own CAD database, as well as data for the silicon wafer providing the InFO connectivity you start to see how messy the CAD flow can get. Also considering each die may have thousands of pins you also realize how easy it would be to get something hooked up wrong and how hard it would be to find a mistake without good LVS tools. This will be a much appreciated addition to the flow.

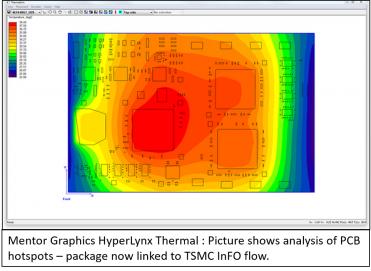

In December of 2016, John was interviewed for an article in Chip Scale Review in which he outlined how TSMC has worked with EDA companies like Mentor to develop EDA solutions for IC and package design with an intent to ensure that InFO designs would be fully compliant with TSMC’s packaging design rules and sign-off requirements. At that time, John mentioned that TSMC was in fact working to expand the InFO tool support  into sign-off electrical analysis to enable designers to analyze the parasitic impacts from InFO and its neighboring layers. It appears this is now in place for the Mentor flow, with the addition of signal integrity checking of the InFO interconnects using signal path tracing, extraction, simulation and netlist export.

into sign-off electrical analysis to enable designers to analyze the parasitic impacts from InFO and its neighboring layers. It appears this is now in place for the Mentor flow, with the addition of signal integrity checking of the InFO interconnects using signal path tracing, extraction, simulation and netlist export.

The flow also now supports integration to thermal analysis and thermally-aware post-layout simulation flows to provide early identification of potential system level heat issues. The connection to the simulation world also enables such things as multi-die reliability analysis including analysis of electromigration and IR drop.

While Fan-Out Wafer Level Processing is catching on with its promises of low cost, small form factors, and low power with high performance, the addition of a fully integrated IC and package design flow goes a long way toward making this a truly usable technology. TSMC is using its extensive expertise in generating process design kits for advanced IC processes along with their significant experience and long historic relationships with EDA players like Mentor Graphics to jump out well ahead of their OSAT (outsource assembly and test) competitors in bringing FOWLP technology into real production use.

See Also:

- TSMC Collaborates with Mentor for New InFO Technology Variants

- Mentor Adds Support for InFO Packaging at TSMC

- FOWLP in the Foundry

- Not yet a fan of fan-out? Why you should be!

- Xpedition Package Integrator

- Calibre Platform and Products

Comments

0 Replies to “Fan-Out Wafer Level Processing Gets Boost from Mentor TSMC Collaboration”

You must register or log in to view/post comments.