At TSMC’s OIP on October 1st, Mentor Graphics have 5 different presentations. Collect the whole set!

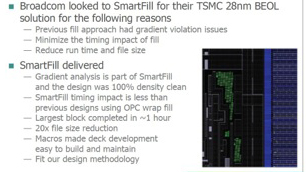

11am, EDA track. Design Reliability with Calibre Smartfill and PERC. Muni Mohan of Broadcom and Jeff Wilson of Mentor. New methodologies were invented for 28nm for smart fill meeting DFM requirements (and at 20nm me may have to double pattern some layers of fill). Also, Calibre PERC for checking subtle electrical reliability rules. These were both successfully deployed on a large 28nm tapeout at Broadcom.

11am, EDA track. Design Reliability with Calibre Smartfill and PERC. Muni Mohan of Broadcom and Jeff Wilson of Mentor. New methodologies were invented for 28nm for smart fill meeting DFM requirements (and at 20nm me may have to double pattern some layers of fill). Also, Calibre PERC for checking subtle electrical reliability rules. These were both successfully deployed on a large 28nm tapeout at Broadcom.

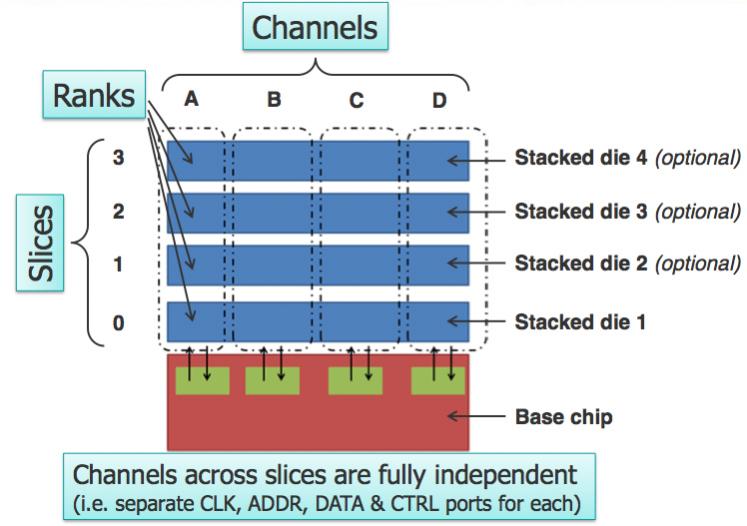

2pm, EDA track. EDA-based Design for Test for 3D-IC Applications. Etienne Racine of Mentor. Lots about how to test 3D and 2.5D ICs such as TSMCs CoWoS. 3D requires bare die testing (to address the known good die problem) via JTAG. This can also be used for contactless leakage test. How to test memory on logic and other test techniques for the More that Moore world of 3DICs.

2pm, EDA track. EDA-based Design for Test for 3D-IC Applications. Etienne Racine of Mentor. Lots about how to test 3D and 2.5D ICs such as TSMCs CoWoS. 3D requires bare die testing (to address the known good die problem) via JTAG. This can also be used for contactless leakage test. How to test memory on logic and other test techniques for the More that Moore world of 3DICs.

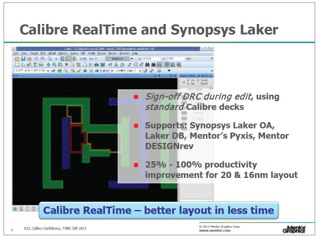

3pm on EDA/IP/Services track. Synopsys Laker Custom Layout and Calibre Interfaces: Putting Calibre Confidence in Your Custom Design Flow. Joseph Davis of Mentor. Synopsys’s Laker layout environment can run Calibre “on the fly” during design to speed creation of DRC correct layouts. Especially at nodes below 28nm, where the rules are incomprehensible to mere mortals this is almost an essential requirement to developing layout in a timely manner.

3pm on EDA/IP/Services track. Synopsys Laker Custom Layout and Calibre Interfaces: Putting Calibre Confidence in Your Custom Design Flow. Joseph Davis of Mentor. Synopsys’s Laker layout environment can run Calibre “on the fly” during design to speed creation of DRC correct layouts. Especially at nodes below 28nm, where the rules are incomprehensible to mere mortals this is almost an essential requirement to developing layout in a timely manner.

4.30pm, EDA track. Advanced Chip Assembly and Design Closure Flow Using Olympus SoC. Karthik Sundaram of nVidia and Sudhakar Jilla of Mentor. Chip assembly and design closure has become a highly iterative manual process with a huge impact on both schedule and design quality. Mentor and nVidia talk about a closure solution for TSMC processes that include concurrent multi-mode multi-corner optimization.

Identifying Potential N20 Design for Reliability Issues Using Calibre PERC. MH Song of TSMC and Frank Feng of Mentor. Four key reliability issues are electro-migration, stress-induced voiding, time-dependent dielectric breakdown of intermetal dielectric, and charge device model ESD. Calibre’s PERC can be used to verify compliance to these reliability rules in the TSMC N20 process.

Full details of OIP including registration are here.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.