Yesterday’s SEMICO IP Ecosystem Conference was well worth the time. Everybody was there: ARM, Synopsys, Cadence, Mentor Graphics, GlobalFoundries, TSMC, MIPS, Tensilica, AMD, Atrenta, Sonics, and Tabula, everybody except Intel of course. What do Intel and I have in common? We don’t play well with others…

First up was Jim Feldham, President of Semico Research with some interesting industry forecast slides. Semiconductor revenue grew 1.3% in 2011 and is predicted to grow 9% in 2012, very believable, even with 28nm wafer allocation. Tablets (+46%) and Smartphones (+34%) lead the way with the SoC market reaching $85B. I agree with this assessment 100%.

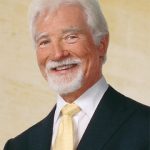

Second up was Warren East, ARM CEO. I like Warren, he is a humble man (like me) and has the traditional British dry sense of humor (unlike me). Warren’s presentations pack the most content you will see from a semiconductor CEO. Since ARM owns 99.99% (exaggeration) of the mobile business their customer surveys are very relevant. Here are some interesting takeaways from Warren’s slides:

- 5B+ People Connected

- $10 Mobile Phones

- Mobile Devices Outsell PCs

- Always On, Always Connected

Warren didn’t mention “He who must not be named” (Intel) but clearly this is a clean shot at them:

- Fabless Model Lowers Costs

- IP is Key: 100+ Blocks Per Chip

- $200M Cost for 14nm SoC

- Design Costs = 52.8% Software + 47.2% Hardware

- Standards Reduce Costs

Taking a “systems” view:

- A vibrant ecosystem is maintained through collaboration and aligned investments

- Tweaks to current models will not solve big challenges or drive significant growth

- Boundaries will need to shift and change, enabling broader IP and services that spread development costs across the chip ecosystem

Bottom line: It’s all about the ecosystem. Linaro is one example as I blogged in Intel Versus ARM (Linaro).

The SoC Design community is dedicated to design engineers developing highly integrated system-on-chip solutions with ARM technology. This site addresses every phase of SoC design, from architecture selection through front end design and back end implementation and manufacturing. Learn more about best practices for designing advanced SoCs based on ARM Cortex processors, Artisan physical IP, CoreLink system IP and ARM Connected Community IP, tools and services.

ARM has a landing page on SemiWiki now which you can find HERE, ARM related blogs are organized there. The theme you will notice is ecosystem and SoC. SemiWiki blogger Don Dingee has a series of blogs on Smart Mobile SoCs including NVIDIA, Apple, Samsung, TI, and Qualcomm. He even did one on Intel: Smart Mobile SoCs: Intel. Don will go to China for the next one so stay tuned!