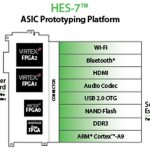

Roaming around the hall at ARM TechCon 2012 left me with eight things of note, but one of the larger ideas showing up everywhere is the Xilinx Zynq. Designers are enthralled with the idea of a dual-core ARM Cortex-A9 closely coupled with programmable logic.… Read More

CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read More

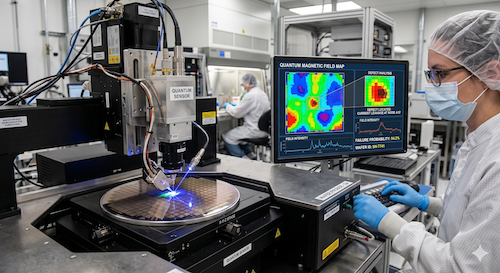

CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read More Sensing. A Quantum Tech Ready for Market?While the quantum world revolves around quantum computing,…Read More

Sensing. A Quantum Tech Ready for Market?While the quantum world revolves around quantum computing,…Read More #DAC2026 Marks Another Pivotal Moment for the Semiconductor IndustryThe 2026 Design Automation Conference (DAC 2026) marks…Read More

#DAC2026 Marks Another Pivotal Moment for the Semiconductor IndustryThe 2026 Design Automation Conference (DAC 2026) marks…Read More IPLM: Future Forward Webinar May 19thStep into the future of semiconductor design management…Read More

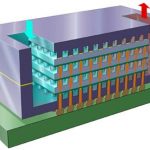

IPLM: Future Forward Webinar May 19thStep into the future of semiconductor design management…Read More3D Architectures for Semiconductor Integration and Packaging

There is obviously a lot going on in 3D IC these days. And I don’t mean at the micro level of FinFETs which is also a way of going vertical. I mean through-silicon-via (TSV) based approaches for either stacking die or putting them on an interposer. Increasingly the question is no longer if this technology will be viable (there… Read More

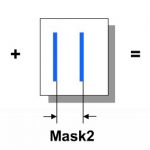

Double Patterning Verification

You can’t have failed to notice that 20nm is coming. There are a huge number of things that are different about 20nm from 28nm, but far and away the biggest is the need for double patterning. You probably know what this is by now, but just in case, here is a quick summary.

Lithography is done using 193nm light. Today we use immersion… Read More

HP Loses Its Autonomy!

HP buys Autonomy for $11B then does an $8.8B writedown?!?!?! Was HP swindled by Autonomy? As a long time HP customer I’m outraged by this behavior. Not just the over priced acquisition but the behavior of HP on a whole! Even today 4 of the 6 laptops in my house are HP as are my printers. How am I supposed to buy HP products with a straight … Read More

Apple Will NOT Manufacture SoCs at Intel

The internet is a funny place where rumors are true and truths are rumors. The latest one has Apple using Intel as a foundry. This is fuel for the rivalry between SemiWiki blogger Ed McKernan and me. Ed says Apple will use Intel, I say Apple will use TSMC, we have a very expensive dinner riding on this one.

How Apple Plans to Leverage Intel’s Foundry

Tim Cook’s strategy to disengage from Samsung as a supplier of LCDs, memory and processors while simultaneously creating a worldwide supply chain from the remnants of former leaders like Sharp, Elpida, Toshiba and soon Intel is remarkable in its scope and breadth. By 2014, Apple should have in place a supply chain for 500M iOS devices… Read More

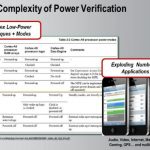

Apache Power Artist Capabilities II

This is the second part of my discussion with Paul Traynar, Apache’s PowerArtist guru. The first part discussed sequential reduction capabilities. Part I was here.

There are two big challenges with doing power analysis at the RTL level. Firstly, how do you get an accurate enough model of what the design will dissipate given… Read More

A Brief History of the MIPS Architecture

MIPS is one of the most prolific, longest-living industry-standard processor architectures, existing in numerous incarnations over nearly three decades.

MIPS has powered products including game systems from Nintendo and Sony; DVRs from Dish Network, EchoStar and TiVo; set-top boxes from Cisco and Motorola; DTVs from Samsung… Read More

Subsystem IP, myth or reality?

I have participated to a panel during IP-SoC, I must say that “Subsystem IP, myth or Reality” was a great moment. The panel was a mix of mid-size IP vendor (CAST, Sonics), one large EDA (Martin Lund from Cadence), Semiwiki blogger and one large IDM (Peter Hirt from STM) who has very well represented the customer side. And, to make the… Read More

Yield Analysis and Diagnosis Webinar

Sign up for a free webinar on December 11 on Accelerating Yield and Failure Analysis with Diagnosis.

The one hour presentation will be delivered via webcast by Geir Eide, Mentor’s foremost expert in yield learning. He will cover scan diagnosis, a software-based technique, that effectively identifies defects in digital logic… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior