Intro

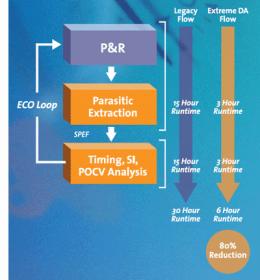

Over the lunch hour on Tuesday at DAC I met with Emre Tuncer, VP – Product Engineering & Applications and heard about extraction and timing analysis.

Notes

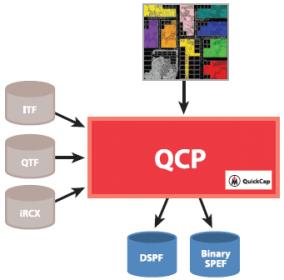

GoldX – parasitic extractor. Fast extractor, recently announced, all new technology, early customer adoption. One customer deploying it in 40nm, soon to be 28nm.… Read More

Build a 100% Python-based Design environment for Large SoC Designs