The mobile devices market is simply exploding, with smartphones shipmentgoing up to the sky, tabletsemerging so fast that some people think it will replace PC (but this is still to be confirmed…). This lead mobile SoC designs to integrate increasingly more features, to support customer needs for more computing power and sophisticated… Read More

The RISC-V and Open-Source Functional Verification ChallengeMost of the RISC-V action at the end…Read More

The RISC-V and Open-Source Functional Verification ChallengeMost of the RISC-V action at the end…Read More Sarcina Democratizes 2.5D Package Design with Bump Pitch Transformers2.5D package design is rapidly finding its stride…Read More

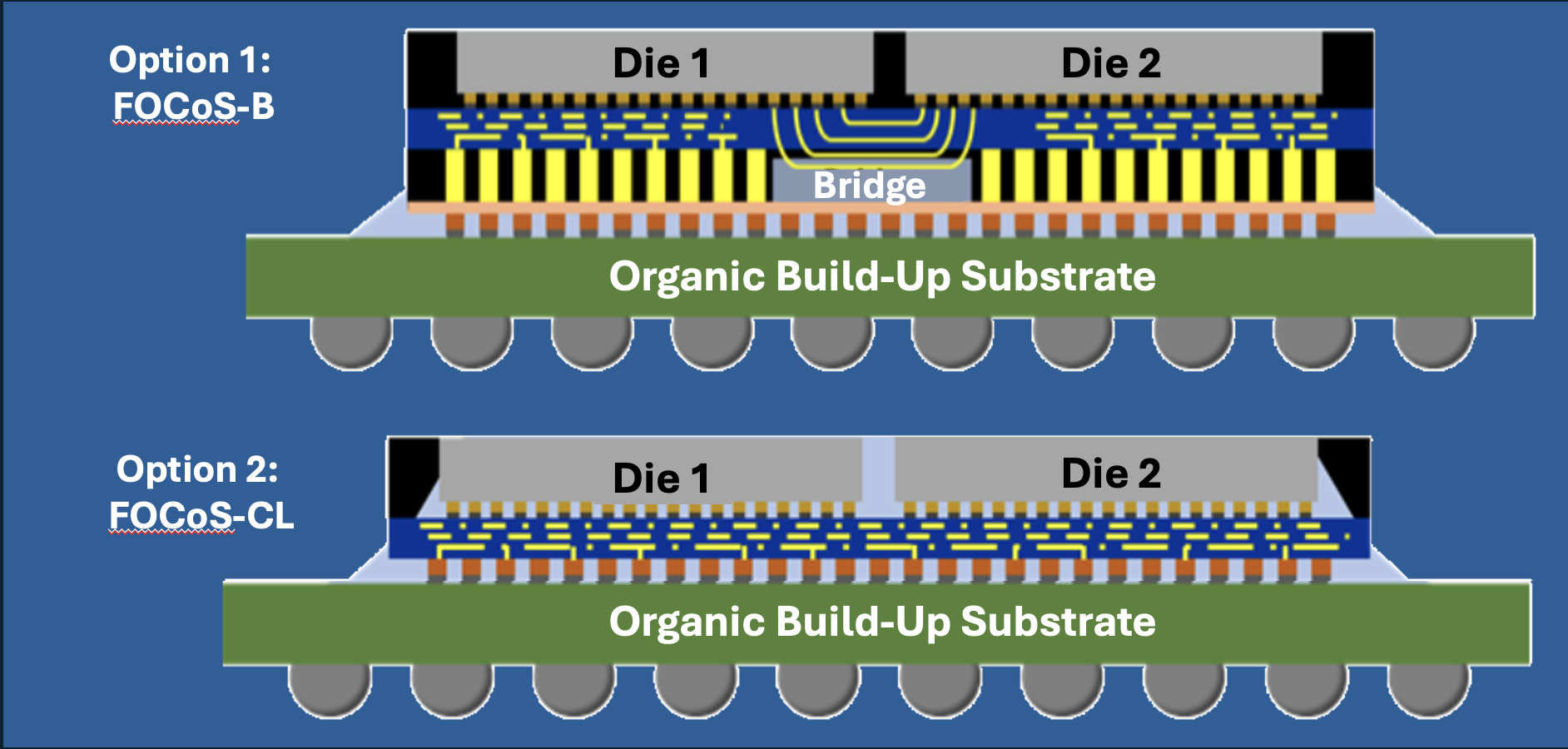

Sarcina Democratizes 2.5D Package Design with Bump Pitch Transformers2.5D package design is rapidly finding its stride…Read More Addressing Reliability and Safety of Power Modules for Electric VehiclesAs electric vehicles (EVs) gain widespread adoption, safety,…Read More

Addressing Reliability and Safety of Power Modules for Electric VehiclesAs electric vehicles (EVs) gain widespread adoption, safety,…Read More Shaping Tomorrow’s Semiconductor Technology IEDM 2024Anyone who has read my articles about IEDM…Read More

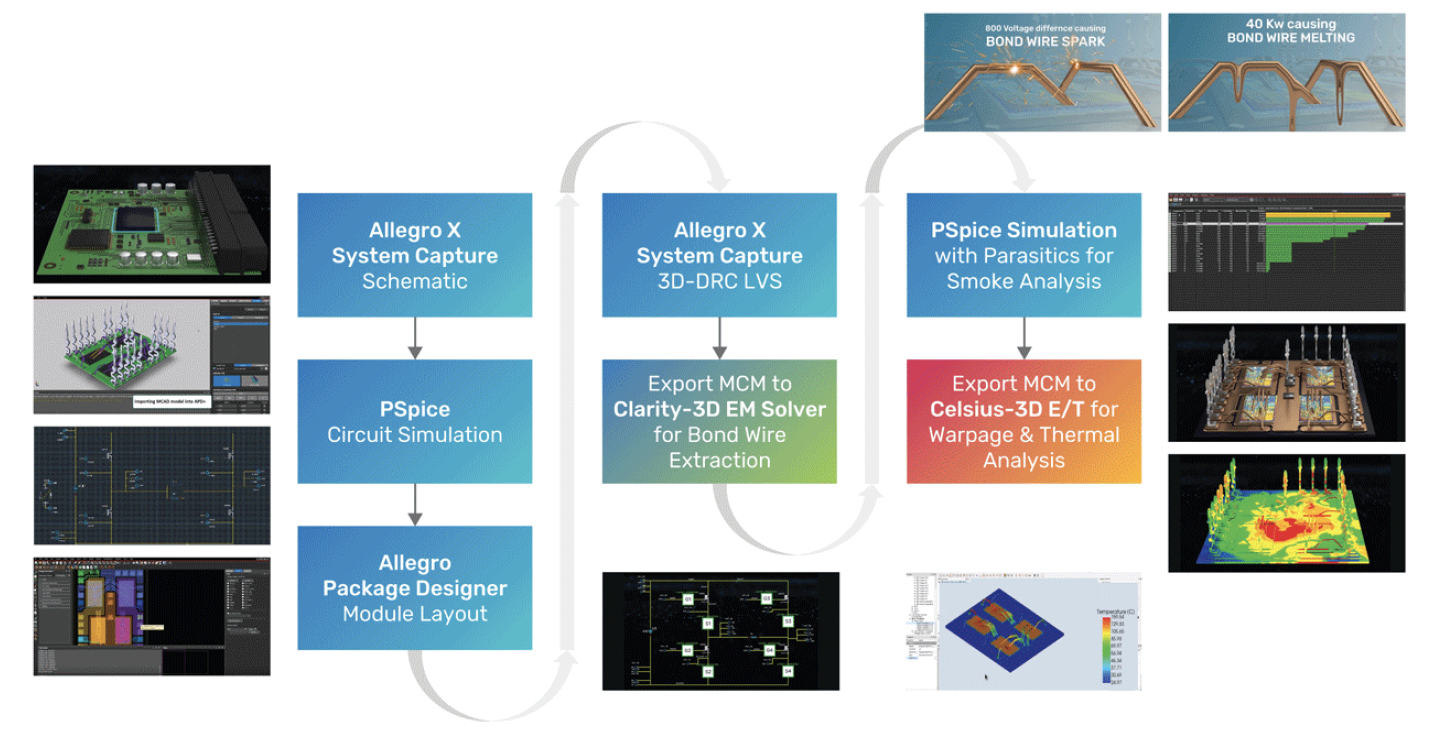

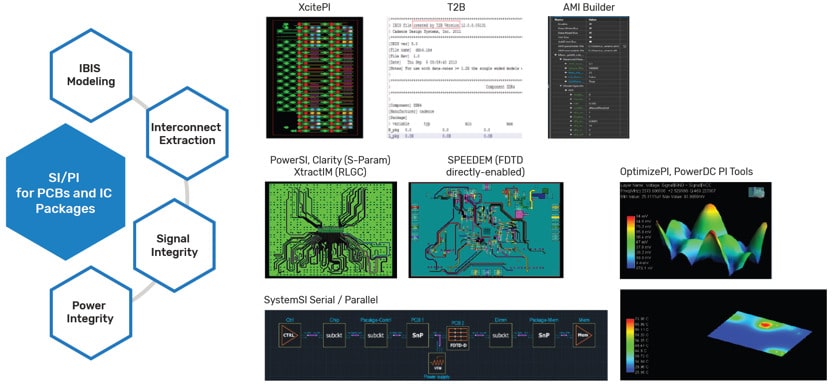

Shaping Tomorrow’s Semiconductor Technology IEDM 2024Anyone who has read my articles about IEDM…Read More SI and PI Update from Cadence on Sigrity XSignal Integrity (SI) and Power Integrity (PI) issues…Read More

SI and PI Update from Cadence on Sigrity XSignal Integrity (SI) and Power Integrity (PI) issues…Read MoreApple Plays Saudi Arabia’s Role in the Semiconductor Market

The retirement of Steve Jobs left most commentators wondering if Tim Cook could lead Apple marching ever onward and upward. In truth, Tim Cook’s contribution on the operations side has been just as instrumental in the destruction of Apple’s PC and consumer electronics competitors as Jobs’ product vision. Under Tim Cook’s guidance,… Read More

Semiconductor equipment spending beginning to decline

Semiconductor manufacturing equipment shipments have leveled off after a strong rebound from the 2008-2009 downturn. August 2011 three-month-average shipments based on combined data from SEMI (North American and European companies) and SEAJ (Japanese companies) were $2.9 billion, down from a peak of $3.2 billion in May … Read More

A Verilog Simulator Comparison

Intro

Mentor, Cadence and Synopsys all offer Verilog simulators, however when was the last time that you benchmarked your simulator against a tool from a smaller company?

I just heard from an RTL designer (who wants to remain anonymous) about his experience comparing a Verilog simulator called CVC from Tachyon against ModelSim… Read More

Apple’s Supply Chain

I am doing some consulting right now for a company that shall remain nameless, and one of the things I have had to look at is Apple’s supply chain. I came across an interesting article by someone with the goal to “buy a MacBook Air that isn’t made by Apple.” He is in the UK and doesn’t like Apple’s… Read More

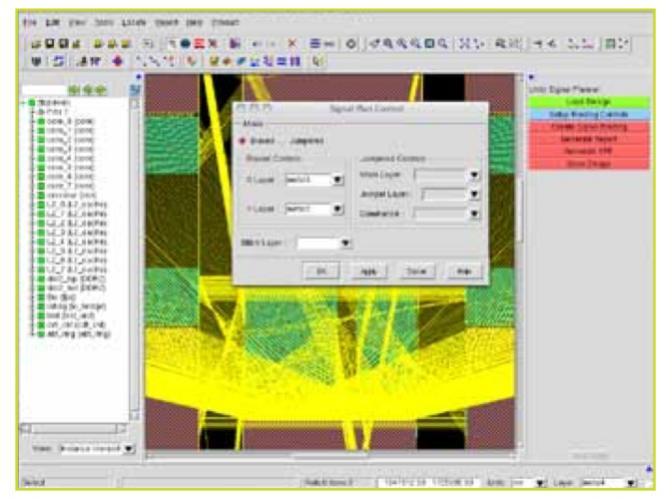

Custom Signal Planning Methodologies

It is no secret that custom ICs are getting larger and more complex and this has driven chip design teams to split up into smaller teams to handle the manual or semi-automated routing of the many blocks and hierarchical layers that go to make up such a design. These sub-teams don’t just need to handle the routing within their own block(s)… Read More

Analog Constraint Standards

Over the years there has been a lot of standard creation in the IC design world to allow interoperability of tools from different vendors. One area of recent interest is interoperable constraints for custom IC design. Increasingly, analog design layout is becoming more automated. Advanced process nodes require trial layouts… Read More

Coby Hanoch joins Jasper

Jasper has hired Coby Hanoch as the VP of international sales to manage sales outside of North America. I talked to him last week.

Coby started his career after graduation from the Israeli Institute of Technology as an engineer at National Semiconductor. He quickly ended up in verification where they developed the first random … Read More

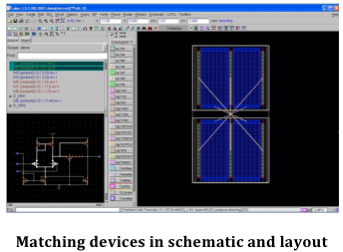

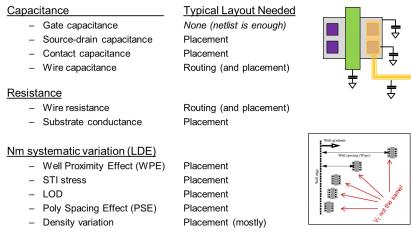

Nanometer Circuit Verification: The Catch-22 of Layout!

As analog and mixed-signal designers move to very advanced geometries, they must grapple with more and more complex considerations of the silicon. Not only do nanometer CMOS devices have limitations in terms of analog-relevant characteristics such gain and noise performance, but they also introduce new sources of variation… Read More

AMS Design, Optimization and Porting

AMS design flows can follow a traditional path or consider trying something new. The traditional path goes along the following steps:

[LIST=1]

AI Semiconductor Market