Silicon dominates our lives, CPU’s, GPU’s are in the limelight but the unsung hero is the FPGA. They simply do the work where other silicon dare not tread, as they are unfit for the task. Never send a boy to do a man’s job.

For a moment, if we can, just for a few minutes perhaps we can break away from the social media bubble… Read More

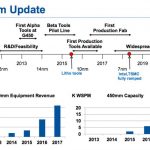

ASML High-NA EUV is Not Ready for High-Volume Production