The presentations from the 450mm sessions at SEMICON West are up now. After talking to equipment manufacturers and the foundries I’m fairly confident 450mm wafers will be under our Christmas trees in 2016, absolutely. TSMC just increased CAPEX again and you can be sure 450mm is part of it. SEMI has a 450mm Central landing page HERE… Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More

Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor TechnologyAlchip Technologies has recently reported significant progress in…Read More

Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor TechnologyAlchip Technologies has recently reported significant progress in…Read More CapEx Up for Foundry, MemorySemiconductor Intelligence estimates total semiconductor industry capital spending…Read More

CapEx Up for Foundry, MemorySemiconductor Intelligence estimates total semiconductor industry capital spending…Read MoreCompressing OpenGL ES textures

The 80s called, and they want lazy programming back. Remember “Mr. Mom”? Michael Keaton is talking about rewiring the house, and Martin Mull asks if he’s going to use all 220V, and Keaton responds “Yeah, 220, 221, whatever it takes.” Not knowing what’s inside can make you look silly.

Such is the case with OpenGL ES. Taking a look at … Read More

An EDA Acquisition that Worked

I first heard about Andrew Yang back in 1993 when he founded a Fast SPICE company called Anagram, then acquired by Avant! in 1996. Andrew’s latest EDA company Apache Design, Inc.was started in 2001, then acquired by ANSYS in 2011. Most EDA mergers simply don’t work because of one or more reasons, like:

- Incompatible

Save the Dates

There are several events in Silicon Valley coming up of general interest to people working in EDA and the semiconductor industry.

SEMI 16th Annual Valley Lunch Forum. August 22nd, 11.30am to 1.30pm, Santa Clara Marriott

- What are the Opportunities for Advanced Semiconductor Devices?

- Where will the year end for 2013?

- Will we have

Wanna Buy A Blackberry?

So Blackberry (formerly known as Research In Motion or RIM) is up for sale. Basically, apart from some cash in the bank, its main value now seems to be patents and, perhaps, some security technology. The murderers are in Cupertino and Mountain View, Apple’s iPhone (and iPad) and Google’s Android along with its licensees,… Read More

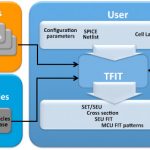

How Resistant to Neutrons Are Your Storage Elements?

There are two ways to see how resistant your designs are to single-event errors (SEE). One is to take the chip or even the entire system and put it in a neutron beam and measure how many problems occur in this extreme environment. While that may be a necessary part of qualification in some very high reliability situations, it is also … Read More

Electronic System Level: Gary Smith

Gary Smith has been talking about how the electronic system level (ESL) is where the future of EDA lies as design teams move up to higher levels encompassing IP blocks, high level synthesis, software development using virtual platforms and so on. At DAC this year in Austin he talked about how the fact that EDA controls the modeling… Read More

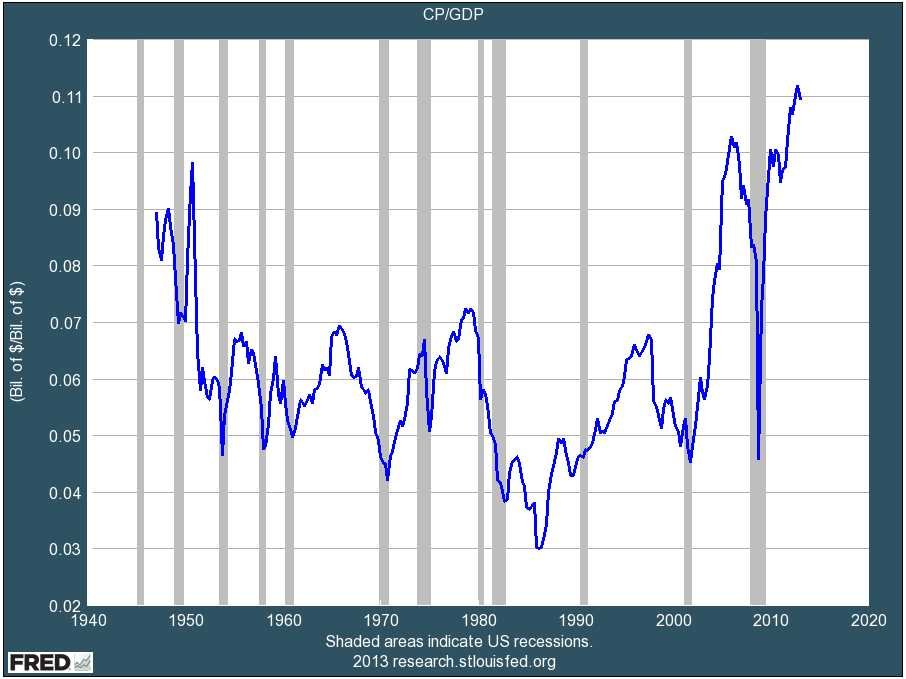

The Most Disturbing Economic Graphs Ever!

After driving to Silicon Valley for the past 30 years I am acutely aware of traffic patterns and to me that directly relates to the economy. The recession of 2009 really hit traffic patterns with what I would estimate as a 20% unemployment rate in Silicon Valley. I could leave my home in Danville anytime of the day and have no traffic … Read More

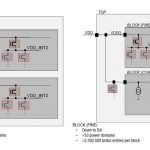

RTL Design For Power

My Samsung Galaxy Note II lasts about two days on a single battery charge, which is quite the improvement from the Galaxy Note I with only a one day battery charge. Mobile SoCs are being constrained by battery life limitations, and consumers love longer-laster devices.

There are at least two approaches to Design For Power:

- Gate-level

Robust Design <- Robust Flow <- Robust Tools

I could have written the sequence of the title in reverse order, but no, design is the one which initiates the need of a particular flow and the flow needs support of EDA tools to satisfy that need. It’s okay if the design is small; some manual procedures and workarounds/scripts may be able to perform certain jobs. However, as the design… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center