Xilinx just announced the shipment of the first TSMC based 20 nm FPGAs, beating Altera to the punch yet again. Xilinx was also the first to ship TSMC 28nm FPGAs and will undoubtedly beat Altera to 14nm which could be the knockout punch we have all been waiting for. The Xilinx UltraScale is a new family of FPGAs that will use 20nm and 16nm… Read More

Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read More

Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read More Scaling Multi-Die Connectivity: Automated Routing for High-Speed InterfacesThis article concludes the three-part series examining key…Read More

Scaling Multi-Die Connectivity: Automated Routing for High-Speed InterfacesThis article concludes the three-part series examining key…Read More Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read MoreSemiconductor Fabrication Module Optimization

The growing process integration complexity at each technology node has increased development time and cost, and this trend looks to continue. There is a looming risk of delivering unrepeatable critical unit processes (or process modules) that would require revisiting development and manufacturing requalification or in … Read More

The Pelican Has Landed: Formal on an Unannounced ARM Processor

At the Jasper Users’ Group, Alex Netterville of ARM presented about how ARM are using formal on an unannounced processor code-named Pelican. Don’t read the presentation trying to find out information about Pelican itself, there isn’t any. That wasn’t the topic. Alex has been using formal approaches… Read More

IP-SoC 2013 Top Class Presentations…

… were given to an ever shrinking audience. This is IP-SoC paradox: audience has enjoyed very good presentations made by TSMC (for the first time at IP-SoC, as far as I remember), SMIC, D&R, Gartner or ST-Microelectronic, to name just a few. The event is well organized, on the morning you can listen to keynotes in the largest … Read More

Can Intel Catch Samsung? Can Anybody Catch Samsung?

As a professional conference attendee I see a lot of keynotes, some good and some bad. I saw a great one from Kurt Shuler at the SEMICO IP Impact Conference last week. Why this conference was not standing room only I do not know. Kurt’s characterization of the semiconductor industry was well worth the price of admission. I didn’t actually… Read More

Running Multiple Operating Systems: Hypervisors

How do you run multiple operating systems on the same processor? You use virtualization and you run a hypervisor underneath all the so-called “guest” operating systems. So what is virtualization?

Virtualization started with VM/370 developed in 1972 at IBM (the current version is still in use). Here is how it works.… Read More

Debugging Complex Embedded System – How Easy?

In today’s world of semiconductor design with SoCs having complex IPs, hardware and software working together on a single chip, it’s hard to imagine a system without embedded software into it. But it is easy to guess how difficult it would be to test that hardware and software embedded system. And often there is limited window of … Read More

Data Management in Russia

Milandr is a company based in Moscow that makes high reliability semiconductor components for the aerospace, automotive and consumer markets, primarily in Russia. They work with multiple foundries, including X-FAB and TSMC in technologies from 1um down to 65nm. Corporate headquarter and main IC design house is located in Russian… Read More

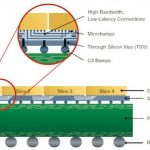

Xilinx and TSMC: Volume Production of 3D Parts

A couple of weeks ago, Xilinx and TSMC announced the production release of the Virtex-7 HT family, the industry’s first heterogeneous 3D ICs in production. With this milestone, all Xilinx 28nm 3D IC families are now in volume production. These 28nm devices were developed on TSMC’s Chip-on-Wafer-on-Substrate (CoWoS)… Read More

TSMC on Semiconductor IP Quality

It is important to note that the System On Chip (SoC) revolution that is currently driving mobile electronics has one very important enabling technology and that is Semiconductor Intellectual Property. Where would we be without the commercial IP market segment? Computers and phones would still be on our desks for one thing, and… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era