The number one semiconductor IP company in the world is ARM, and they have really figured out how to use social media in a big way to communicate with and listen to their customers. When you first visit the Home page for ARM there are four social media icons displayed in monochrome underneath the menu bar. As you hover over the icons (Twitter,… Read More

Hardware is the Center of the Universe (Again)The 40-Year Evolution of Hardware-Assisted Verification — From…Read More

Hardware is the Center of the Universe (Again)The 40-Year Evolution of Hardware-Assisted Verification — From…Read More Smarter ECOs: Inside Easy-Logic’s ASIC Optimization EngineEasy-Logic Technology Ltd. is a specialized Electronic Design…Read More

Smarter ECOs: Inside Easy-Logic’s ASIC Optimization EngineEasy-Logic Technology Ltd. is a specialized Electronic Design…Read More The Name Changes but the Vision Remains the Same – ESD Alliance Through the YearsThe Electronic System Design Alliance (ESDA) has been…Read More

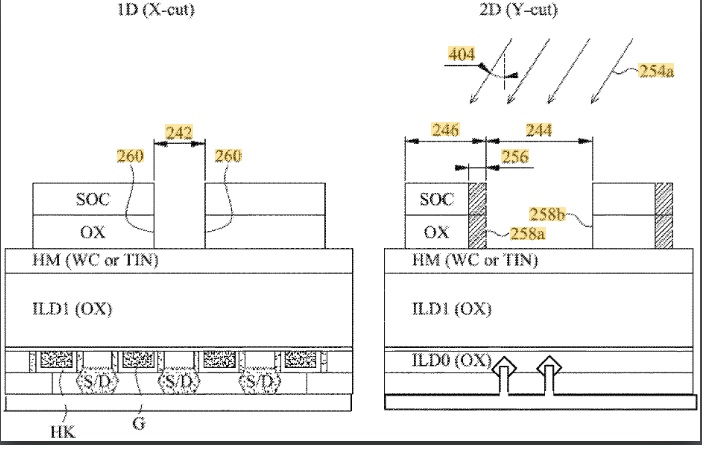

The Name Changes but the Vision Remains the Same – ESD Alliance Through the YearsThe Electronic System Design Alliance (ESDA) has been…Read More TSMC Process Simplification for Advanced NodesIn the modern world, the semiconductor industry stands…Read More

TSMC Process Simplification for Advanced NodesIn the modern world, the semiconductor industry stands…Read More CEO Interview with Juniyali Nauriyal of PhotonectJuniyali Nauriyal is the CEO and Co-Founder of…Read More

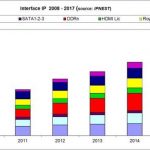

CEO Interview with Juniyali Nauriyal of PhotonectJuniyali Nauriyal is the CEO and Co-Founder of…Read MoreWhat’s new in the “Interface IP Survey” ?

The reader will find many updates in the “Interface IP Survey” from IPNEST, released in October 2013. Good question, as the IP market is a very fast moving one and the protocol based Interface IP, is moving even faster… exhibiting 20% growth rate in 2012, expected to grow with 10% CAGR between 2012 and 2017 to reach $700M. … Read More

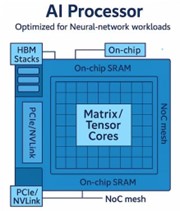

Semiconductor Process Development: A View from the Trenches at IEDM

There is always a lot of posturing and pontificating when semiconductor executives talk about the future of process development. They are fighting an air war of perception and investor expectations, so naturally want to make sure they have plenty to brag about. But, as we pointed out recently with Intel’s problems at 14nm, moving… Read More

Front-End Design Summit: Physically Aware Design

Save closure time and boost performance by incorporating knowledge of physically aware design early into your front-end design implementation flow

With the adoption of advanced process nodes, design closure is becoming increasingly difficult due to the lack of convergence between the front end and the back end of the register-transfer… Read More

Intel’s Mea Culpa!

The Intel analyst meeting last week reads like an absolute train wreck with INTC stock dropping 5%+ the very next day. Since I work in the fabless semiconductor ecosystem during the day I was not able to listen to it live like the other pundits. Nor am I as easily fooled by Power Point slides. I did however review the materials and would… Read More

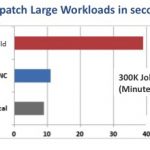

Better License Usage vs More Licenses

When you see a new product announcement from an EDA company, it is always put in terms that make it seem as if the engineer is sitting at his or her desktop with a big server and is running the new tool to wondrous effect. But the reality in the real world is that most companies have a computing infrastructure of server farms, often several… Read More

Signoff Summit and Voltus

Yesterday Cadence had an all-day Signoff Summit where they talked about the tools that they have for signoff in advanced nodes. Well, of course, those tools work just fine in non-advanced nodes too, but at 20nm and 16nm there are FinFETs, double patterning, timing impacts from dummy metal fill, a gazillion corners to be analyzed… Read More

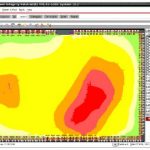

Thermal Analysis for 3D SoC Integration

The first time that I saw a DRAM in a ceramic package running on a tester I made the mistake of touching my finger to the metal lid, scorching my finger and teaching me a lesson that ICs can run extremely hot. I’ve read a lot the past few years about 3D IC design, and immediately my mind becomes curious about how an engineer would go… Read More

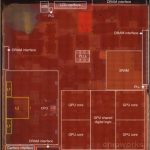

It’s about the mobile GPU memory bandwidth per watt, folks

There has been a lot of huffing and puffing lately about 64-bit cores making it into the Apple A7 and other mobile SoCs, and we could probably dedicate a post to that discussion. However, there are a couple other wrinkles to the Apple A7 that should be getting a lot more attention.

There are two primary causes of user frustration in multimedia… Read More

QCOM delivers first TSMC 20nm mobile chips!

QCOM is now sampling the TSMC 20nm version of its market dominating Gobi LTE modem. The announcement also included a new turbo charged version of their 28nm Snapdragon 800 SoC with a Krait 450 quad core CPU and Adrino 420 GPU. Given the comparable benchmarks between the Intel 22nm SoC and the 28nm SoCs from Apple and QCOM, the new 20nm… Read More

CEO Interview with Aftkhar Aslam of yieldWerx