You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Mentor is acquiring Oasys, subject to all the usual caveats about shareholder and regulatory approval. The shareholder paperwork went out earlier this week. The common stock is valueless so presumably the price is low (and Mentor historically has not paid high prices for its acquisitions).

So what is going to happen with the technology?… Read More

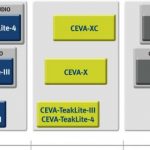

Our popular smart phones have a whole slew of RF-based radios in them for: Bluetooth, WiFi, LTE, GSM, NFC. Using just a single clock frequency for a DSP function or SoC is a thing of the past, so the design of multirate systems is here to stay. So now the challenge on the design and verification side is to use a methodology that supports:… Read More

AMD Goes 3Dby Paul McLellan on 12-13-2013 at 7:16 pmCategories: EDA

I attended the 3D packaging conference in Burlingame this week. The most interesting presentation to me was by Bryan Black of AMD. He argued very convincingly that Moore’s Law is basically over for the PC microprocessor business and the way forward is going to be 3D. AMD are clearly working on all this.

Increased density and… Read More

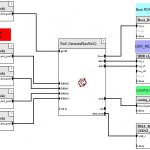

Interconnect plays a significant role in the semiconductor design of a SoC; if not architected and handled well, it can lead to an overdesigned SoC impacting on its power, performance and area. Since a SoC generally contains multiple IPs requiring different data paths to satisfy varying latency and performance cycles, it has … Read More

The smartphone is becoming a commodity, a lifecycle stage where the strong get stronger, the weak get weaker, and the products standardize and start to look alike. This dynamic is driving innovation in existing products to extremes and spawning a new class of wearable devices.

Today two major players are leading the mobile hardware… Read More

This week Xilinx has announced that “The Xilinx 20nm All Programmable UltraScale™ portfolio is now available with detailed device tables, product documentation, design tools and methodology support.”

Do you know what 20nm is? It’s small, tiny. Think about it this way, as I just learned today that one nanometer is about as long… Read More

Jim Feldhan, President of Semico Research presented earlier this month at the Impact Conference on the topic: Focus on the IP Ecosystem. I’ve reviewed his 19 page presentation, and summarize it with:

- End markets like smart phones and tablets are dominant

- Growth drivers include the Internet of Things (IoT)

- World semi forecast

…

Read More

Donald Rumsfeld categorized what we knew into known unknowns and unknown unknowns. In a chip design, those unknown unknowns can bite you and leave you with a non-functional design, perhaps even intermittent failures which can be among the hardest problems to debug.

Chips are too big to do any sort of full gate-level simulation,… Read More

My very first thought when hearing about HSPICE is using it for IC simulation at the transistor-level, however it can also be used to simulate a package or PCB interconnect very accurately, like in the PCB layout of a DDR3 system where timing is critical. I attended a webinar this morning that was jointly presented by Zuken and Synopsys… Read More

As a full time financial writer/investor, I am always on the lookout for compelling risk/reward opportunities, particularly in small-cap tech. While the world of large-cap tech is generally well understood by the investment/analyst community, smaller cap names are usually under-followed and often misunderstood. One such… Read More

Intel’s Pearl Harbor Moment