On February 3, 2026, Andes Technology officially announced the launch of RISC-V Now!, a new global conference series designed around the next phase of RISC-V adoption: real-world deployment and commercial scaling. This initiative marks a shift from exploratory and research-focused events toward practical, production-oriented… Read More

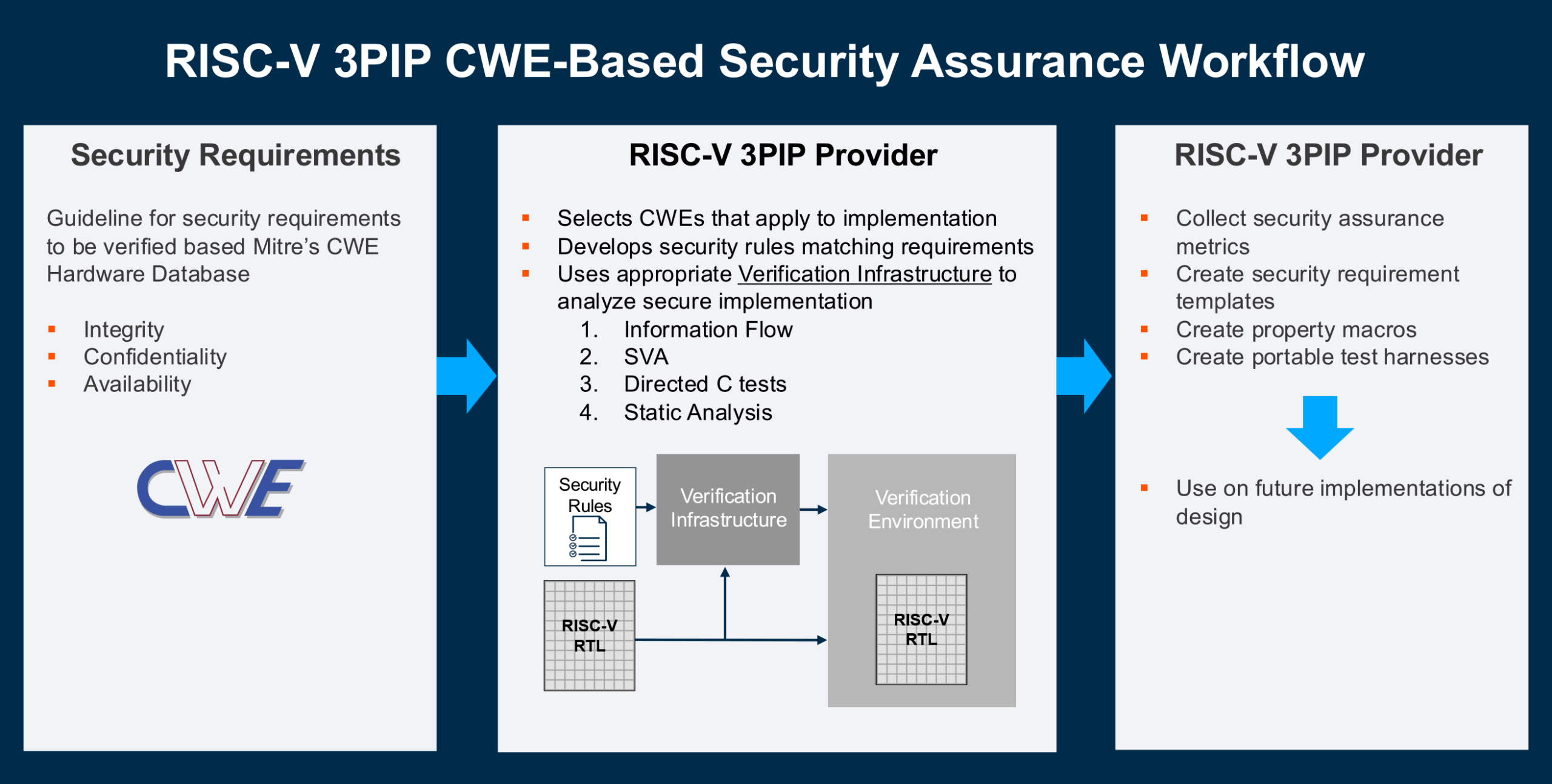

Securing RISC-V Third-Party IP: Enabling Comprehensive CWE-Based Assurance Across the Design Supply Chainby Jagadish Nayak RISC-V adoption continues to accelerate…Read More

Securing RISC-V Third-Party IP: Enabling Comprehensive CWE-Based Assurance Across the Design Supply Chainby Jagadish Nayak RISC-V adoption continues to accelerate…Read More Apple’s iPhone 17 Series 5G mmWave Antenna Module Revealed to be Powered by Soitec FD-SOI SubstratesRecent independent teardown and technical analyses have confirmed…Read More

Apple’s iPhone 17 Series 5G mmWave Antenna Module Revealed to be Powered by Soitec FD-SOI SubstratesRecent independent teardown and technical analyses have confirmed…Read More Advancing Automotive Memory: Development of an 8nm 128Mb Embedded STT-MRAM with Sub-ppm Reliability IEDM 2025 Papers MRAM…Read More

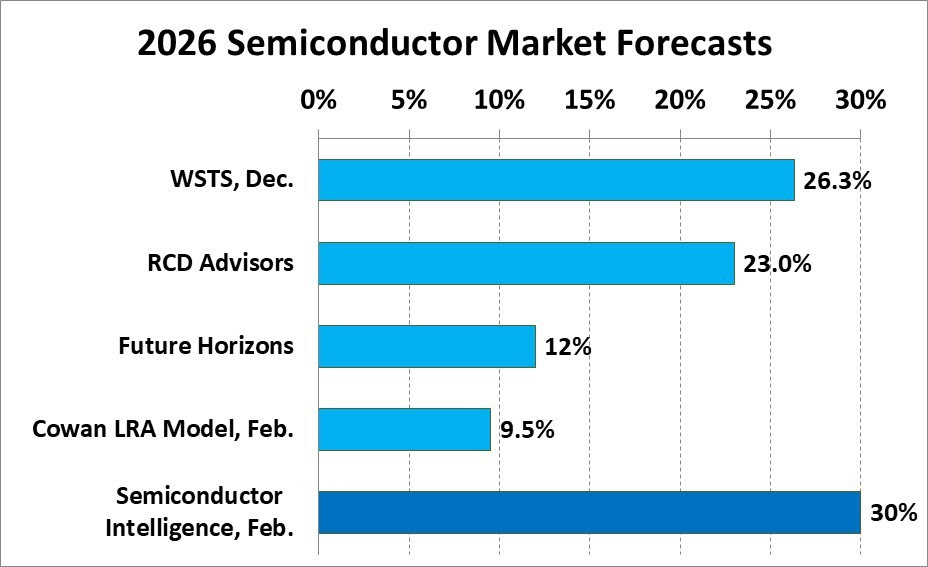

Advancing Automotive Memory: Development of an 8nm 128Mb Embedded STT-MRAM with Sub-ppm Reliability IEDM 2025 Papers MRAM…Read More AI Drives Strong Semiconductor Market in 2025-2026The global semiconductor market in 2025 was $792…Read More

AI Drives Strong Semiconductor Market in 2025-2026The global semiconductor market in 2025 was $792…Read More How Customized Foundation IP Is Redefining Power Efficiency and Semiconductor ROIAs computing expands from data centers to edge…Read More

How Customized Foundation IP Is Redefining Power Efficiency and Semiconductor ROIAs computing expands from data centers to edge…Read MoreNanoIC Extends Its PDK Portfolio with First A14 Logic and eDRAM Memory PDK

NanoIC has announced a major expansion of its process design kit portfolio with the introduction of its first A14 logic and embedded eDRAM memory PDK. This milestone reflects the company’s growing role in enabling advanced semiconductor design at cutting-edge technology nodes and addresses increasing industry demand for… Read More

2026 Outlook with Coby Hanoch of Weebit Nano

Coby Hanoch is the CEO of Weebit Nano. Coby has nearly 45 years’ of experience in the semiconductor and related industries, including engineering, engineering management, sales, and executive roles. Coby was previously CEO at PacketLight Networks, and held VP Worldwide Sales roles at both Verisity and Jasper Design Automation.… Read More

How Switzerland Built a Global Semiconductor Edge by Thinking Smaller

By Alain-Serge Porret, Vice President, Integrated & Wireless Systems, CSEM

Since ramping up several years ago, the global semiconductor and artificial intelligence (AI) race has been driven by scale, from building larger data centers, developing bigger and more powerful models, and with them, increasingly complex and… Read More

How 25G Ethernet, PCIe 5.0, and Multi-Protocol PHYs Enable Scalable Edge Intelligence

Physical AI is changing how intelligent systems interact with the real world. These systems must sense, process, and respond to data in real time. Unlike cloud AI, Physical AI depends on fast local processing and reliable distributed communication. This shift creates a new challenge. Systems must move large volumes of sensor… Read More

The 71st International Electron Devices Meeting (IEDM 2025)

It is hard to believe this conference is older than most all of the participants, including myself. The amount of history behind this conference is amazing. Back in 1955 the meeting began as the Electron Devices Meeting (EDM), organized by what later became the IEEE Electron Devices Society. Its core purpose was to bring together… Read More

Advances in ATPG from Synopsys

I first learned about ATPG – Automatic Test Program Generation in the 1980s at Silicon Compilers, then continued in the 90s at Viewlogic with the Sunrise tools, so it was illuminating to get an update from Synopsys on their ATPG technology by attending a webinar. Synopsys over the years has developed a family of test tools, shown … Read More

TSMC’s 2026 AZ Exclusive Experience Day: Bridging Careers and Semiconductor Innovation

In February of 2026, Taiwan Semiconductor Manufacturing Company (TSMC) will host the TSMC AZ Exclusive Experience Day in Phoenix, Arizona, offering selected participants a rare opportunity to engage directly with one of the most advanced semiconductor manufacturing organizations in the world. The event will serve as an immersive… Read More

DAC – The Chips to Systems Conference 2026

The Design Automation Chips to Systems Conference is the preeminent international event for professionals involved in electronic design, system architecture, and EDA. Formerly known simply as the Design Automation Conference or DAC has evolved over more than six decades into a forward-looking forum that spans the entire… Read More

CEO Interview with Naama BAK of Understand Tech

Naama BAK is an entrepreneur with 15 years of experience in tech. He is the founder of Understand Tech, a generative AI platform for enterprises, and Trustii.io, a machine learning platform for data science challenges. He previously held roles at NXP Semiconductors, Orange, and Safran, working in cybersecurity across research,… Read More

An AI-Native Architecture That Eliminates GPU Inefficiencies