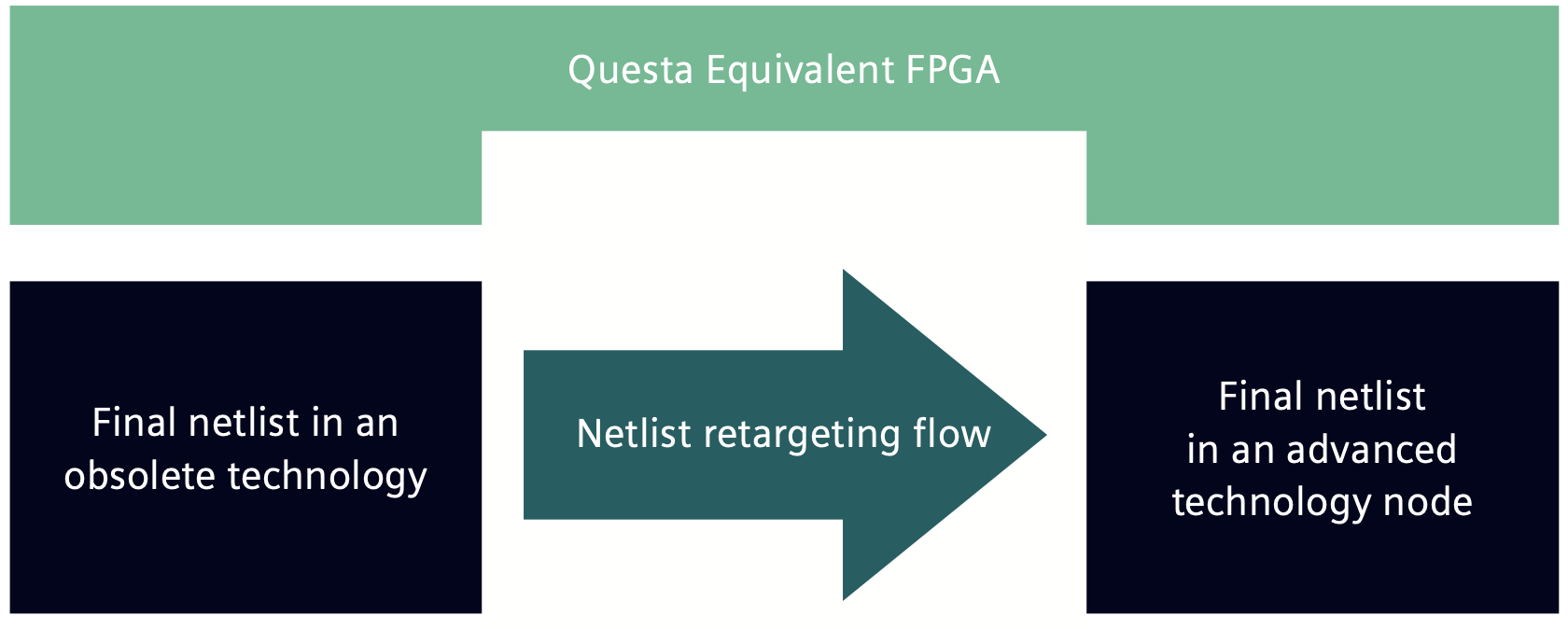

The complexity of System-on-Chip (SoC) designs continues to rise at an accelerated rate, with design complexity doubling approximately every two years. This increasing complexity makes verification a more difficult and time-consuming task for design engineers. Among the key verification challenges is managing reset domain… Read More

PQShield Demystifies Post-Quantum Cryptography with Leadership LoungePost-Quantum Cryptography, or PQC provides a technical approach…Read More

PQShield Demystifies Post-Quantum Cryptography with Leadership LoungePost-Quantum Cryptography, or PQC provides a technical approach…Read More Datacenter Chipmaker Achieves Power Reduction With proteanTecs AVS ProAs semiconductor technology advances and nodes continue to…Read More

Datacenter Chipmaker Achieves Power Reduction With proteanTecs AVS ProAs semiconductor technology advances and nodes continue to…Read More The Next LLM Architecture? Innovation in VerificationLLMs have amazing capabilities but inference run times…Read More

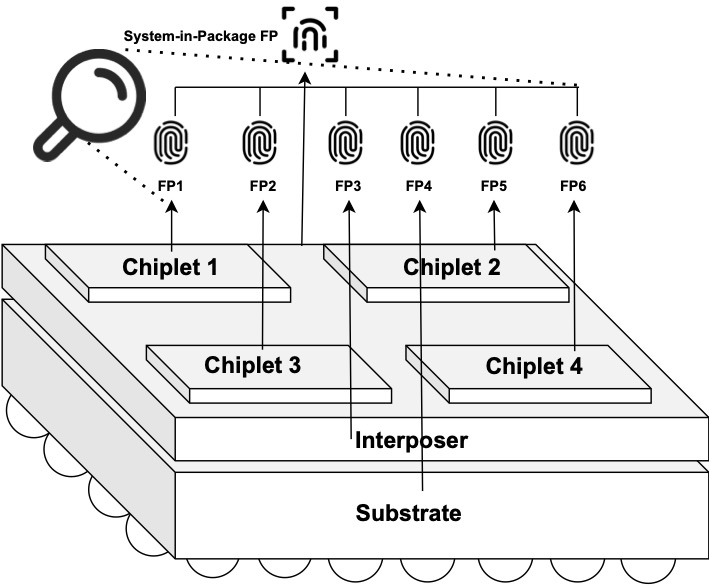

The Next LLM Architecture? Innovation in VerificationLLMs have amazing capabilities but inference run times…Read More Defect-Pattern Leveraged Inherent Fingerprinting of Advanced IC Package with TRIIn the quest to secure the authenticity and…Read More

Defect-Pattern Leveraged Inherent Fingerprinting of Advanced IC Package with TRIIn the quest to secure the authenticity and…Read MoreTSMC 16th OIP Ecosystem Forum First Thoughts

Even though this is the 16th OIP event please remember that TSMC has been working closely with EDA and IP companies for 20+ years with reference flows and other design enablement and silicon verification activities. The father of OIP officially is Dr. Morris Chang who named it the Grand Alliance. However, Dr. Cliff Hou is the one … Read More

The Immensity of Software Development and the Challenges of Debugging Series (Part 2 of 4)

Part 2 of this 4-part series reviews the role of virtual prototypes as stand-alone tools and their use in hybrid emulation for early software validation, a practice known as the “shift-left” methodology. It assesses the differences among these approaches, focusing on their pros and cons.

Safety Grading in DNNs. Innovation in Verification

How do you measure safety for a DNN? There is no obvious way to screen for a subset of safety-critical nodes in the systolic array at the heart of DNNs. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and now Silvaco CTO) and I continue our series on research ideas.… Read More

Collaboration Required to Maximize ASIC Chiplet Value

It is a well-known fact that chiplets provide several advantages over traditional monolithic chips. Despite these benefits, the transition to a chiplet-based design paradigm presents challenges that need coordinated efforts across the industry. In essence, collaborative efforts among various players involved are not … Read More

Andes Technology is Expanding RISC-V’s Horizons in High-Performance Computing Applications

By: Dr. Charlie Su, President and CTO, Andes Technology Corp.

At Andes Technology, we are excited to share some of our latest advancements and insights into the growing role of RISC-V in several high-performance applications. According to the SHD Group report, “IP Market RISC-V Market Report: Application Forecasts in… Read More

Synopsys Powers World’s Fastest UCIe-Based Multi-Die Designs with New IP Operating at 40 Gbps

As the demand for higher performance computing solutions grows, so does the need for faster, more efficient data communication between components in complex multi-die system-on-chip (SoC) designs. In response to these needs, Synopsys has introduced the world’s fastest UCIe-based IP solution, capable of operating at a groundbreaking… Read More

PQShield Builds the First-Ever Post-Quantum Cryptography Chip

Quantum computing promises to deliver vast increases in processing power. The technology exploits the properties of quantum mechanics to create revolutionary increases in performance. Medical and material science research are examples of fields that will see dramatic improvement when production-worthy quantum computers… Read More

Podcast EP248: The Far-Reaching Impact of Finwave Technology With Dr. Pierre-Yves Lesaicherre

Dan is joined by Dr. Pierre-Yves Lesaicherre. Before joining Finwave as CEO, Dr. Lesaicherre was the president, CEO and a director of Nanometrics , a leading provider of advanced process control metrology and software analytics. He also held the CEO position for Lumileds, an integrated manufacturer of LED components and automotive… Read More

CEO Interview: Adam Khan of Diamond Quanta

Adam Khan is a pioneer in diamond semiconductor technology, renowned for his foresight and expertise. As the founder of AKHAN Semiconductor, he played a crucial role in innovating lab-grown diamond thin-films for various applications, such as enhancing smartphone screens and lenses with Miraj Diamond Glass® and improving… Read More

AI Semiconductor Market