Sometimes a standard is a victim of its own success, at least for a while as the economics catch up to the technology. When a standard like USB 3.0 is announced, with a substantial performance increase over USB 2.0, some of the use cases come on board right away. Others, where vendors enjoy a decent ROI with good-enough performance,… Read More

How Customized Foundation IP Is Redefining Power Efficiency and Semiconductor ROIAs computing expands from data centers to edge…Read More

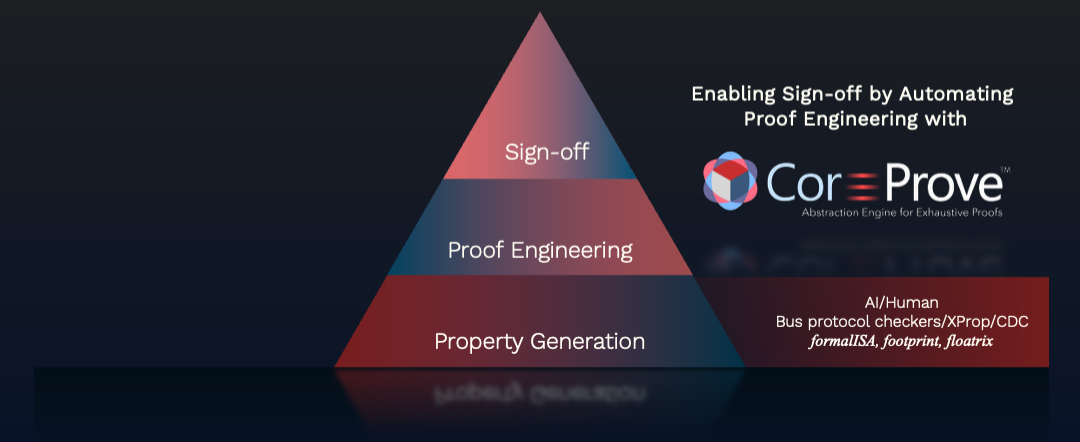

How Customized Foundation IP Is Redefining Power Efficiency and Semiconductor ROIAs computing expands from data centers to edge…Read More Akeana Partners with Axiomise for Formal Verification of Its Super-Scalar RISC-V CoresAkeana Inc. announced a key milestone in the…Read More

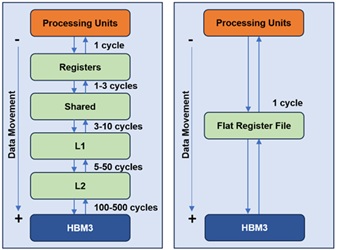

Akeana Partners with Axiomise for Formal Verification of Its Super-Scalar RISC-V CoresAkeana Inc. announced a key milestone in the…Read More An AI-Native Architecture That Eliminates GPU InefficienciesA recent analysis highlighted by MIT Technology Review…Read More

An AI-Native Architecture That Eliminates GPU InefficienciesA recent analysis highlighted by MIT Technology Review…Read More Caspia Technologies Unveils A Breakthrough in RTL Security Verification Paving the Way for Agentic Silicon SecurityIn a significant advancement for the semiconductor industry,…Read More

Caspia Technologies Unveils A Breakthrough in RTL Security Verification Paving the Way for Agentic Silicon SecurityIn a significant advancement for the semiconductor industry,…Read More Designing the Future: AI-Driven Multi-Die Innovation in the Era of Agentic EngineeringAt the 2026 Chiplet Summit, Synopsys presented a…Read More

Designing the Future: AI-Driven Multi-Die Innovation in the Era of Agentic EngineeringAt the 2026 Chiplet Summit, Synopsys presented a…Read MoreVlang – Opportunities Galore for Productivity & Performance

Yes, verification technologies are open to innovation for improved productivity and performance in the face of ever growing SoC/IP design sizes and complexities. There is not much scope left in processor speed to improve, other than multi-core processors in servers which again need software properly architected to be thread-able… Read More

Learning Cache Coherency and Cache Coherent Interconnects: ARM White Paper

Cache Coherency is the type of concept that you think you understand, until you try to explain it. It could be wise to come back to fundamentals, and ask what does coherency means to an expert. I have surf the web, found several white papers on ARM site, and now I can try to share these fresh lessons learned (or you may prefer to download… Read More

SEMulator3D: GlobalFoundries Process Variation Reduction

At SEMICON last month, Rohit Pal of GlobalFoundries gave a presentation on their methodology for reducing process variation. It was titled Cpk Based Variation Reduction: 14nm FinFET Technology.

Capability indices such as Cpk is a commonly used technique to assess the variation maturity of a technology. It looks at a given parameter’s… Read More

Enable a new generation of connected devices?

Imagination Technologies has designed a complete environment to address the needs of emerging IoT and other connected devices, FlowCloud. The technology has been engineered by Imagination to optimize device to cloud connectivity for embedded applications. FlowCloud is a cloud based application independent development… Read More

Intel 14nm is NOT in Production Yet!

Okay, maybe I’m the only one questioning Intel 14nm yield but I think it will be an interesting discussion in the comments section. Here are the questions I would have asked Intel during their recent 14nm PR tour: Has the P1272 process been rolled out to the production fabs in OR, AZ, and Ireland? Is the process officially in production… Read More

FD-SOI at 14nm

At the recent Semicon West, Michel Haond of ST Microelectronics had a presentation on 14nm FD-SOI, or what they more lengthily call UTBB FD-SOI (which when you expand it all out comes to Ultra Thin Body and Buried-Oxide Fully Depleted Silicon on Insulator). When Chenming Hu (or whoever in his group) came up with the term FinFET it … Read More

Another debug view in the UVM Toolbox

One of the biggest endearing qualities of a debug environment for any type of coding is availability of multiple ways to accomplish a task. Whether the preference is keyboard shortcuts, mouse left-click drill-down and right-click pull-down menus, source code view, hierarchical class view, or graphical relationship view, … Read More

How to Reduce Maximum Power at RTL Stage?

Of course that reduction has to stay throughout the design cycle up to layout implementation and fabrication. Since the advent of high density, mega functionality SoC designs at advanced nodes and battery life critical devices played by our fingertips, the gap between SoC power requirement and actual SoC power has only increased.… Read More

Cadence Completes Power Signoff Solution with Voltus-Fi

You probably remember Cadence introduced Voltus towards the end of last year at their signoff summit. This was aimed at digital designers. Prior to that they had announced Tempus, their static timing analysis tool. More recently they announced Quantus QRC extraction. All of these tools that end in -us have been re-architected… Read More

Memory Matters: Signals from the 2025 NVM Survey