Many years ago I read a great little book by Rudy Rucker called “Infinity and the Mind”. This book attempts to explain the many classes of mathematical infinity (cardinals) to non-specialists. As he gets to the more abstract levels of infinity, the author has to resort to an analogy to give a feel for extendible and other cardinal … Read More

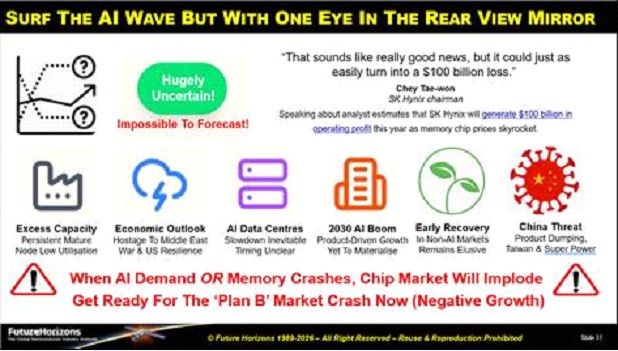

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!May’s WSTS Report saw March’s total monthly semiconductor…Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!May’s WSTS Report saw March’s total monthly semiconductor…Read More SiFive’s P570 Gen 3 Pushes RISC-V Further Into the AI EraWith the launch of its new P570 Gen…Read More

SiFive’s P570 Gen 3 Pushes RISC-V Further Into the AI EraWith the launch of its new P570 Gen…Read More CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read More

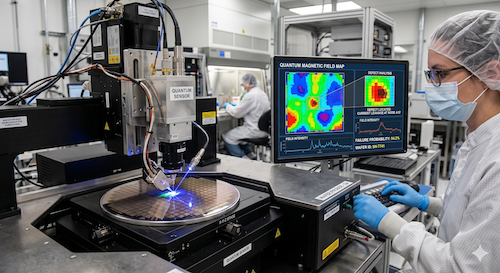

CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read More Sensing. A Quantum Tech Ready for Market?While the quantum world revolves around quantum computing,…Read More

Sensing. A Quantum Tech Ready for Market?While the quantum world revolves around quantum computing,…Read MoreWebinar alert – another break in the memory wall

A couple months ago we heard from another vendor in a webinar on HBM and breaking through the “memory wall”. Next week Open Silicon weighs in on the topic in a webinar with partners SK Hynix and Synopsys.… Read More

Top Ten #53DAC Highlights

Here is a very subjective list of the Top 10 logistical and technical highlights from DAC’53.

(10) With DAC attendance down from its peak days, the Austin Convention Center served as an excellent venue. There was good participation from companies with design centers in the “Silicon Hills”. And, I saw colleagues from Silicon Valley,… Read More

The Evolution of Emulation

Mentor hosted a panel on emulation in their booth at DAC this year. One thing I really liked about this panel is that it didn’t include anyone from Mentor. Not that I have anything against Mentor employees, who are a fine bunch of people from those I know, but I find panels most interesting when the discussion is purely among customers.… Read More

Six Reasons to Rethink Power Semiconductor Packaging

In my 40 years’ experience in power semiconductors I have visited thousands of customers, big and small, on every continent except Antarctica. When the issue invariably turns to the packaging of the power semiconductor – transistor, diode, or integrated circuit – the requests for improvement fall into six categories:

… Read More

3 reasons why diode-based ESD protection ruins the IoT experience

The ‘Dual diode’ approach is one of the most used on-chip and off-chip concept for ESD protection of IO interfaces. It is simple to implement, smaller than any other IO/ESD concept, has a low parasitic capacitance and low leakage.… Read More

New NVIDIA Tesla M10 Could Drive Enterprise VDI Reassessment

NVIDIA is well known for its leadership in graphics processors (GPUs) for gaming, but their business is quickly diversifying with significant growth in other areas like their datacenter and automotive businesses. Within the datacenter, NVIDIA has been evangelizing a vision for a number of years about the benefits of GPUs for… Read More

AMD Brings More Console Features To PC Gaming

Advanced Micro Devices made a big press splash when they won all three major game console platforms. Their presence inside the Microsoft Xbox One, Sony PS4 and Nintendo Wii U has benefited the company financially at the operating income level and has governed how they design their future GPUs. As Advanced Micro Devices has remained… Read More

The CyberSecurity Emperor Has No Clothes

In the past year, I’ve written numerous articles that have a common theme: the security world is badly broken as crypto schemas developed in the 90’s are no defense for today’s sophisticated hackers. For the most part, my blogs have been very well received, and have been picked up and posted by multiple sites and publications worldwide.… Read More

ARM sets up quagmire-free ecosystem for IoT

Wandering around DAC this week, I found much of the discussion focused on the EDA community being at an inflection point. How do we get more design starts from new places with new ideas without jeopardizing existing business? It’s not as simple a transition as it sounds.… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior