There is a lot being said about Intel getting the lead back from TSMC with their 18A process. Like anything else in the semiconductor industry there is much more here than meets the eye, absolutely.

From the surface, TSMC has a massive ecosystem and is in the lead as far as process technologies and foundry design starts but Intel is … Read More

Dan is joined by podcast producer and collaborator Mike Gianfagna for Semiconductor Insiders episode 200. Dan and Mike look over the past two years (and 200 podcasts) to develop a top ten list of changes and innovation in the semiconductor industry. There is a lot of back-story detail on each topic in this far-reaching discussion.… Read More

Semiconductor designs have been progressing over time to address wider product varieties and designs with increasing complexity. Organizations have been addressing intense time-to-market pressures by leveraging globally dispersed team resources. The project-centric design methodology, which once worked well with … Read More

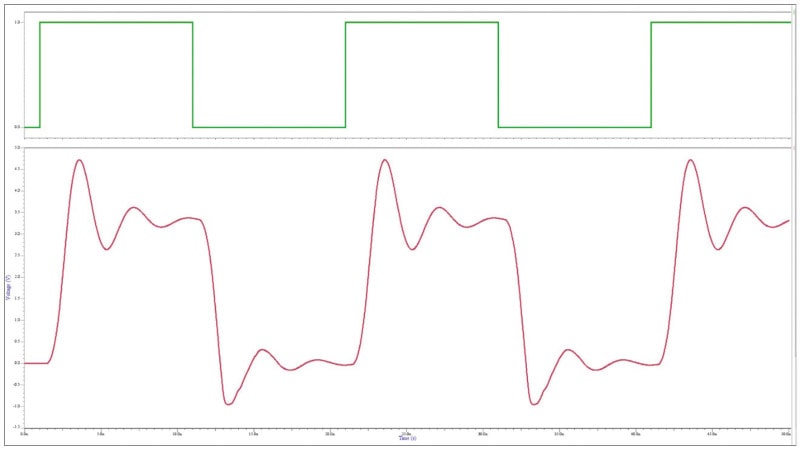

Let’s face it, designs are getting harder, much harder. Gone are the days when the electrical and mechanical design of a system occurred separately. Maybe ten years ago this practice was acceptable. Once the electrical design was completed (either the chip or the board) the parameters associated with the design were then given… Read More

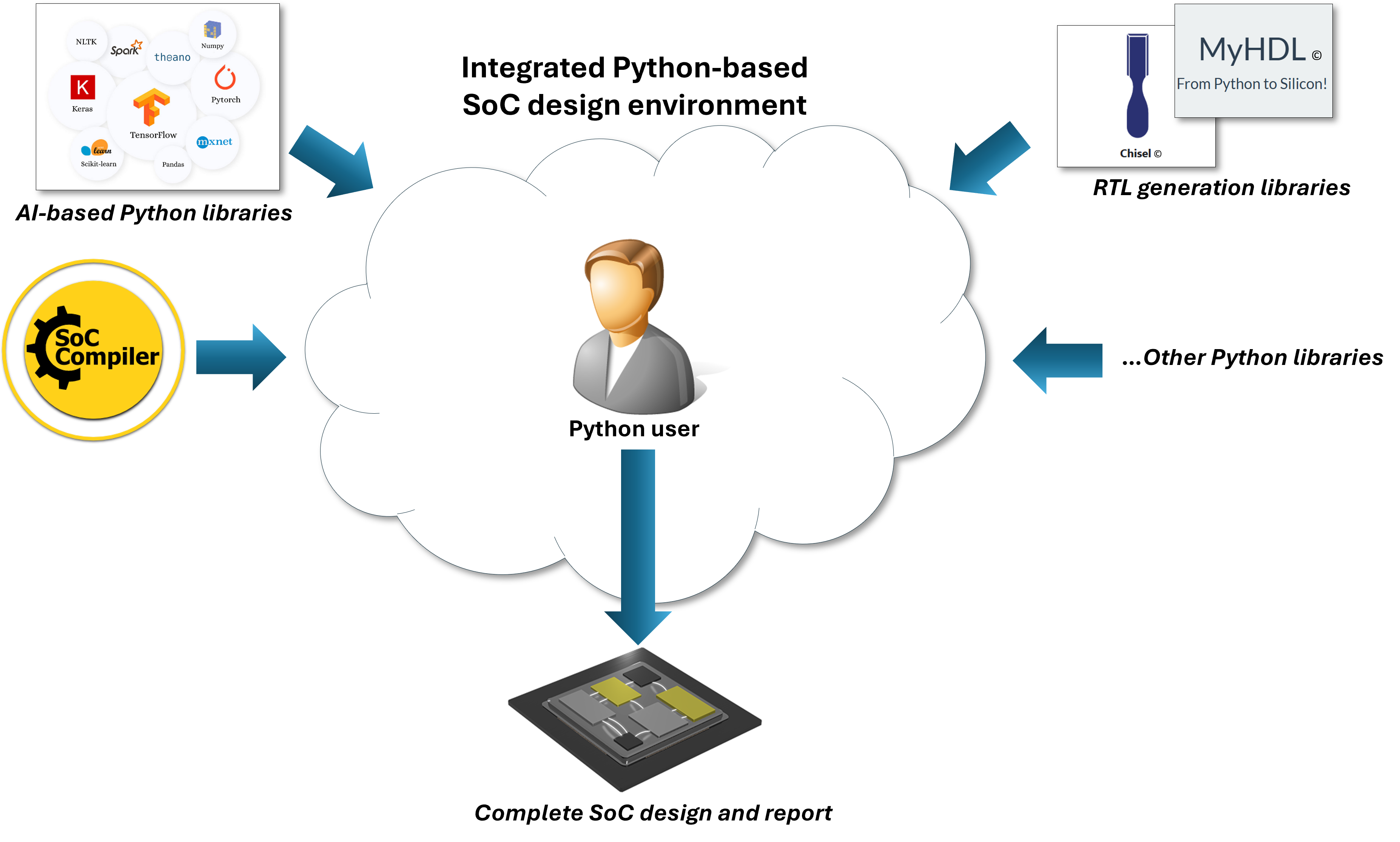

If we look at the semiconductor industry expansion during the last 25 years, adoption of design IP in every application appears to be one of the major factors of success, with silicon technology incredible development by a x100 factor, from 250nm in 2018 to 3nm (if not 2nm) in 2023. We foresee the move to chiplet-based architecture… Read More

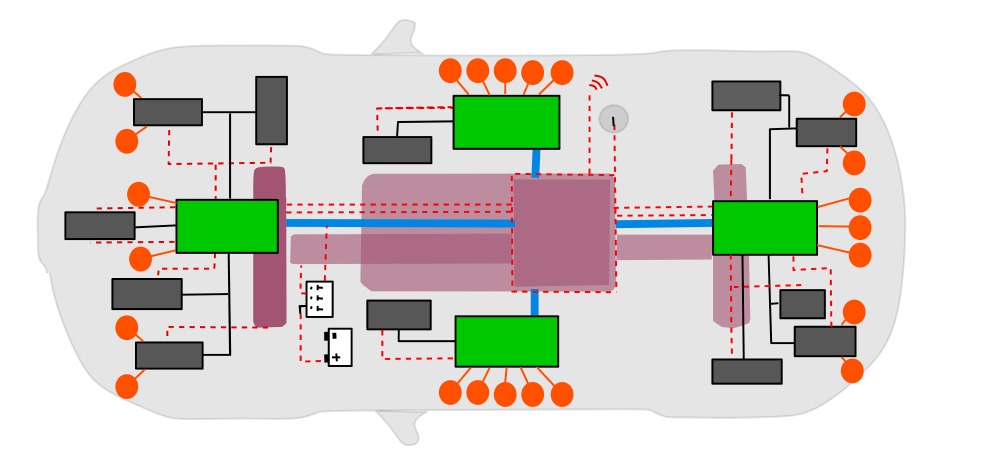

The automotive industry is on the brink of a revolutionary transformation, where predictive maintenance and monitoring are taking center stage. In a recent webinar panel session, industry experts delved into the challenges, current approaches, and future innovations surrounding the guarantee and extension of mission profiles.… Read More

Explicit and implicit sneak paths to leak or compromise information continue to represent a threat to security. This paper looks a refinement of existing gate level information flow tracking (IFT) techniques extended to RTL, encouraging early-stage security optimization. Paul Cunningham (Senior VP/GM, Verification at … Read More

The Universal Verification Methodology (UVM) is a popular way to help verify SystemVerilog designs, and it includes a configuration system that unfortunately has some speed and usage issues. Rich Edelman from Siemens EDA wrote a detailed 20-page paper on the topic of how to avoid these issues, and I’ve gone through it to… Read More

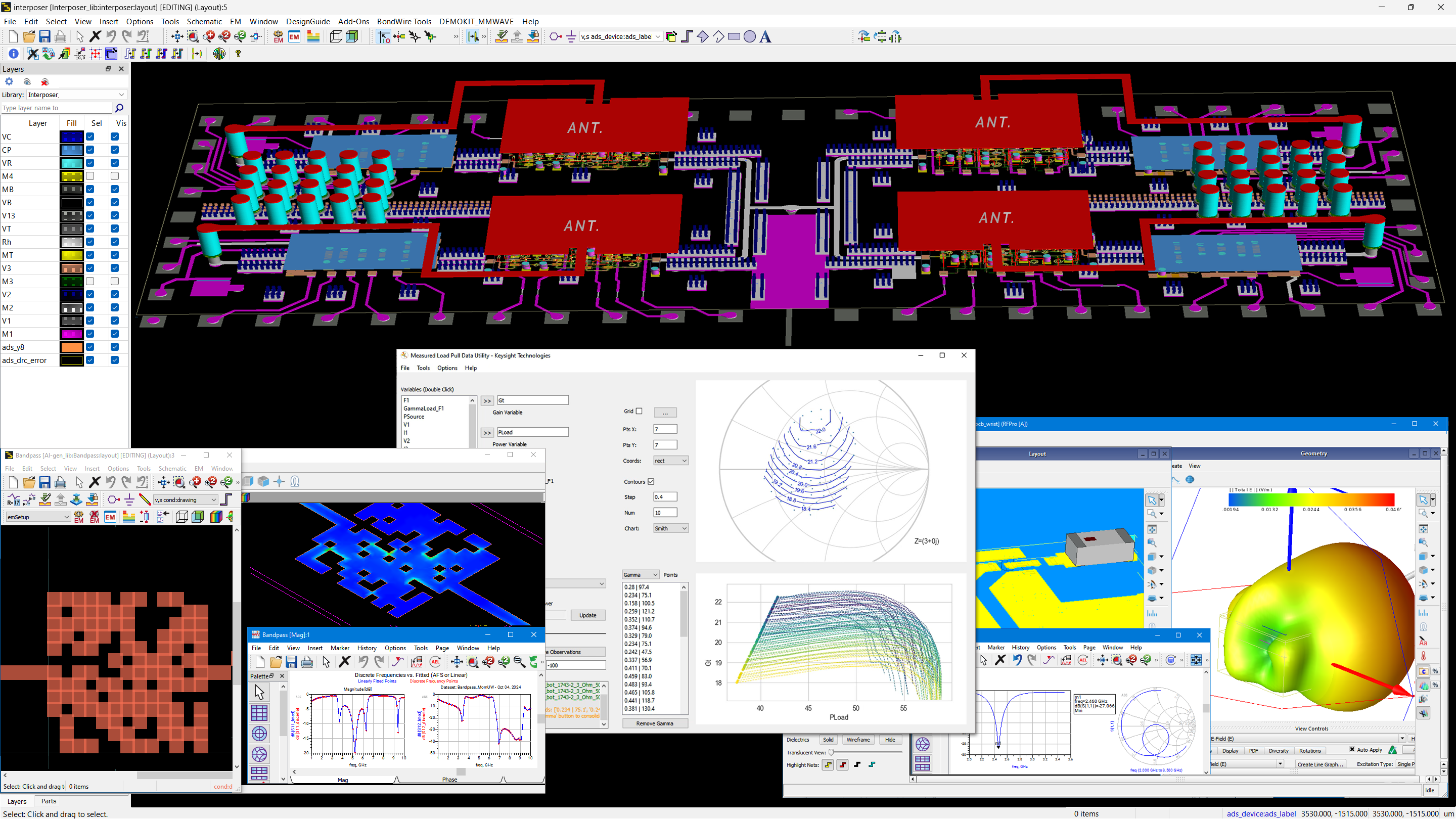

Preventing the propagation of systematic defects in today’s semiconductor design-to-fabrication process requires many validation, analysis and optimization steps. Tools involved in this process can include design rule checking (DRC), optical proximity correction (OPC) verification, mask writing and wafer printing… Read More

On a DRAM chip, the patterning of features outside the cell array can be just as challenging as those within the array itself. While the array contains features which are the most densely packed, at least they are regularly arranged. On the other hand, outside the array, the regularity is lost, but the in the most difficult cases, … Read More

Next Generation of Systems Design at Siemens