Synopsys hosts a regular lunch at DVCon each year (at least over the last few years I have checked), a nice meal and a show, opening a marketing update followed by 2-3 customer presentations on how they use Synopsys verification in their flows. This year’s event was moderated by Piyush Sancheti from Synopsys Verification marketing… Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More

WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More

WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read MoreFPGA, Data and CASPA: Spring into AI

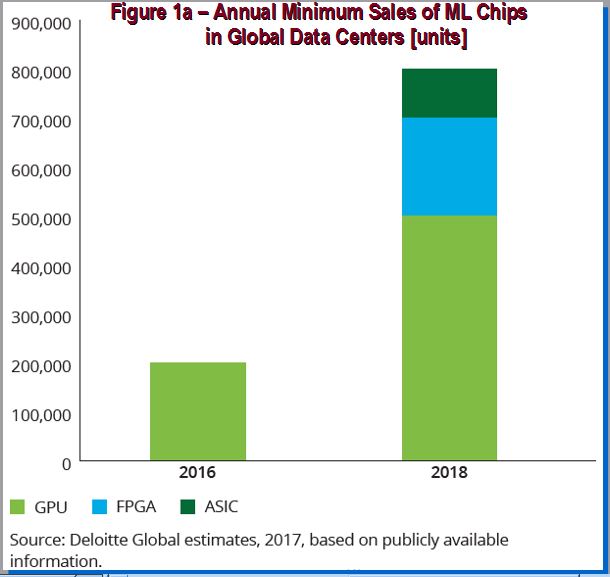

Just like good ideas percolate longer, we have seen AI adoption pace picking-up speed, propelled by faster GPUs. Some recent data points provide good indication that FPGA making a comeback to bridge chip-design needs to keep-up with AI’s ML applications.

According to the Deloitte research firm there is a projected increase of… Read More

Siemens Leverages Mentor Embedded IoT Framework for Industry 4.0

For those of you who wondered at the logic behind Siemens acquisition of Mentor Graphics last year, look no further than a recent announcement by Mentor, now a Siemens business, regarding the release of their new Mentor Embedded IoT Framework (MEIF). To help connect the dots, we need to back up a bit and review a few things about how… Read More

Free Webinar: Silvaco 3D Solver Based Extraction for Device and Circuit Designers

Designers spend a lot of time looking at their layouts in 2D. This is done naturally because viewing in 2D is faster and simpler than in 3D. It helps that humans are good at extrapolating from 2D to 3D. Analysis software, such as extraction software also spend a lot of time looking at layouts in 2D. While this is fine for approximate results,… Read More

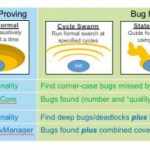

Formal: Going Deep and Going Early

This year I got a chance to talk with Cadence at DVCon on a whole bunch of topics, so expect a steady stream of blogs over the next couple of months. First up was an update from Pete Hardee (Director of Product Management) on, surprise, surprise, formal verification. I’m always trying to learn more about this space, so I picked a couple… Read More

Webinar: Achieve High-performance and High-throughput with Intel based FPGA Prototyping

FPGAs have been used for ASIC prototyping since the beginning of FPGAs (1980s) allowing hardware and software designers to work in harmony developing, testing, and optimizing their products. We covered the history of FPGAs in Chapter 3 of our book “Fabless: The Transformation of the Semiconductor Industry”, which includes … Read More

A Detailed History of Qualcomm

From our book “Mobile Unleashed”, this is a detailed history of Qualcomm:

Chapter 9: Press ‘Q’ to Connect… Read More

Don’t believe the hype about AI in business

To borrow a punch line from Duke professor Dan Ariely, artificial intelligence is like teenage sex: “Everyone talks about it, nobody really knows how to do it, everyone thinks everyone else is doing it, so everyone claims they are doing it.” Even though AI systems can now learn a game and beat champions within hours, they are hard … Read More

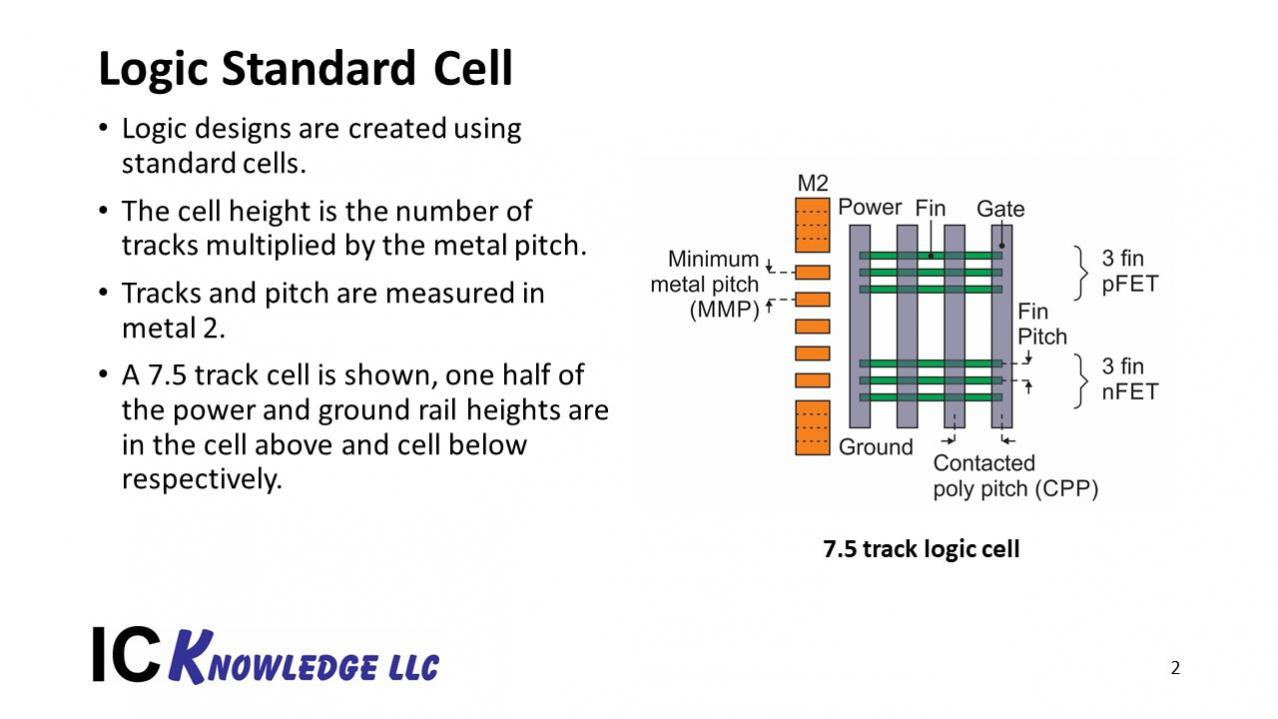

Leading Edge Logic Landscape 2018

The most viewed blogs I write for SemiWiki are consistently blogs comparing the four leading edge logic producers, GLOBALFOUNDRIES (GF), Intel, Samsung (SS) and TSMC. Since the last time I compared the leading edge new data has become available and several new processes have been introduced. In this blog I will update the current… Read More

Self-Driving Car Catch-22 and the Road to 5G

In the novel “Catch-22” from which the eponymous 1970 movie was made we learn of a fictional bureaucratic means by which the U.S. Air Force was able to keep bomber pilots (who might be going crazy) from successfully requesting a release from flying missions based on a medical evaluation. The rationale behind this supposed “catch”… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era