You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

RDC – A Cousin To CDCby Alex Tan on 04-18-2018 at 12:00 pmCategories: Aldec, EDA, FPGA

In a post-silicon bringup, it is customary to bring the design into a known state prior to applying further testing sequences. This is achieved through a Power-on-Reset (POR) or similar reset strategy which translates to initializing all the storage elements to a known state.

During design implementation, varying degrees of… Read More

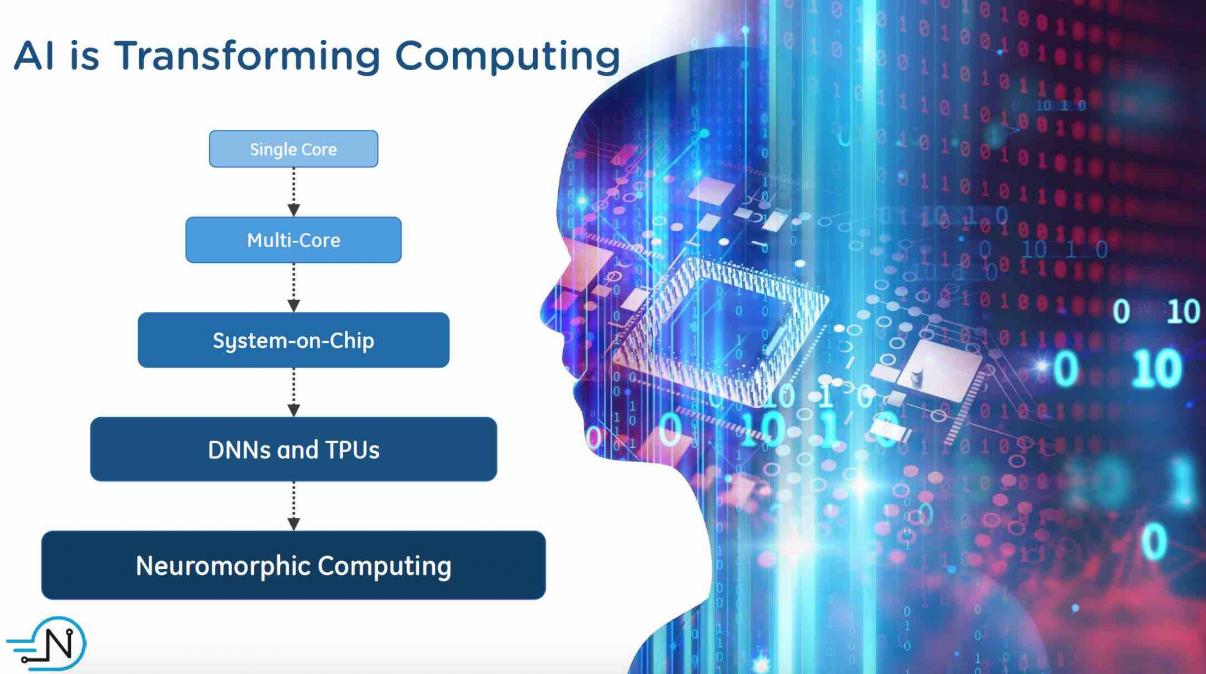

Artificial Intelligence based systems are driving a metamorphosis in computing, and consequently precipitating a large shift in SOC design. AI training is often done in the cloud and has requirements for handling huge amounts of data with forward and backward data connections. Inference usually occurs at the edge and must be… Read More

Cadence has launched the new Tensilica Vision Q6 DSP IP, delivering 1.5x more performance than the former Vision P6 DSP IP and 1.25X better power efficiency. According with Cadence, the mobile industry is moving from traditional feature-based embedded vision to AI-based algorithm, even if all use cases still have mix of vision… Read More

Traditional, rule based, RC extractors rely on a substantial base of assumptions, which are increasingly proving unreliable. Having accurate RC extraction results for parasitic R’s and C’s is extremely important for ensuring proper circuit operation and for optimizing performance and power. Advanced process nodes are making… Read More

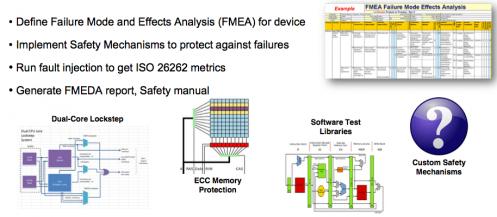

ISO 26262 is serious stuff, the governing process behind automotive safety. But, as I have observed before, it doesn’t make for light reading. The standard is all about process and V-diagrams, mountains of documentation and accredited experts. I wouldn’t trade a word of it (or my safety) for a more satisfying read, but all that … Read More

There is a report in the Seoul Economic Daily that Samsung has completed development of their 7nm process using EUV and that production will begin in June. What is claimed in the report is:

- The process is installed in the Hwaseong S3 Fab

- Samsung has more than 10 EUV systems installed

- Production starts in June with Qualcomm, Xilinx,

…

Read More

The funniest line of the EDA CEO Outlook event was that we should rename our Amazon Echos Wally. Yes Wally is that smart and he remembers pretty much everything. I wish I could rename my Echo Wally because my daughter in-law is named Alexa so we have to turn it off when she is over. The discussion took an interesting turn with EDA in the … Read More

Is Facebook causing the end of happiness?by Vivek Wadhwa on 04-15-2018 at 7:00 amCategories: General

For the past 30 years, most of us around the globe have welcomed modern technology with few questions and fewer reservations. We have treated each new product as a “solution” and paid little attention to its accompanying problems.

The past six months, though, has seen a rapid change of opinion in the United States, … Read More

The theme of this year CDNLive Silicon Valley keynote given by Cadence CEO, Lip-Bu Tan evolves around data and how it drives Cadence to make a transition from System Design Enablement (SDE) to Data Driven Enablement (DDE). Before elaborating further, he noted on some CDNLive conference statistics: 120 sessions, 84% done by users,… Read More

Due to the overwhelming response, here is the first part of the webinar that I did with S2C and a link to the replay. Richard Chang, Vice President of Engineering at S2C did the technical part of the webinar. Richard has a Masters degree in Electrical engineering from the University at Buffalo and more than 20 years experience designing… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center