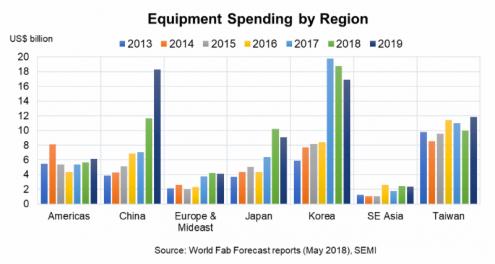

It appears the current cycle has rolled over? The reason is memory & could be worsened by trade Figuring out length, depth and impact of the downturn? We had said that AMAT “called” the top of the cycle on their last conference call even though they may not think so. Semiconductor cycles always ends the same way. The… Read More

Sensors Converge: Where Intelligence Meets the EdgeThe Sensors Converge Conference is one of the…Read More

Sensors Converge: Where Intelligence Meets the EdgeThe Sensors Converge Conference is one of the…Read More Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data CenterAt the TERAFAB launch event in Austin on…Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data CenterAt the TERAFAB launch event in Austin on…Read More Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read MoreMentor at the 55th Design Automation Conference

It’s hard to believe that this is the 55th DAC and even harder to believe that this will be my 35th. So much has changed in 35 years, with DAC back in San Francisco I expect a VERY big crowd and even bigger announcements, absolutely.

Not only is this an epic time for semiconductors, I would say that EDA is exciting again and the Mentor… Read More

Folklore Around the HP 35 LED Development and the Nobel Prize

This is the third in the series of “20 Questions with Wally Rhines”

In the early 1970s I was working on a PhD thesis based upon GaAs light emitting diodes, or LEDs. Many of my predecessors in the Materials Science and Engineering Department at Stanford had worked on other aspects of III-V compounds and some of them went… Read More

Achieving Clean Design Early with Calibre-RTD

Functional and physical verification are easily the two long poles in most IC product developments. During a design implementation cycle, design teams tend to push physical verification (PV) step towards the end as it is a time consuming process and requires significant manual interventions.

PV Challenges

In the traditional… Read More

What to Expect from Methodics at DAC

I’ve been visiting DAC for decades now, at first as an EDA vendor and since 2004 as a freelance EDA consultant. There’s always a buzz about what’s new, semiconductor industry trends, who is getting acquired and the latest commercial EDA and IP offerings. There’s so much vying for my attention at DAC each… Read More

ANSYS at DAC

I’m not going to be at DAC this year because I scheduled a fishing trip at the end of June, assuming the show would stay true to form as an early/mid-June event. Still, having to endure salmon and halibut fishing in Alaska rather than slogging around Moscone Center, I can’t pretend to be too disappointed; I’ll be thinking of you all 😎.… Read More

HOT Party for a Cause at DAC 55

The Design Automation Conference (DAC), now in its 55[SUP]th[/SUP] year, always offers a lively mix of activities. For EDA vendors and their customers, the focus is on the exhibit floor and in booth suites where the latest technology is on display. For R&D engineers and academics, the technical sessions dig deeply into an … Read More

The Wolper Method

If you read around topics in advanced formal verification you’re likely to run into something called Wolper coloring, or what Vigyan Singhal (Chief Oski at Oski) calls the Wolper method. Many domains have specialized techniques but what’s surprising in this instance is a seeming absence of helpful on-line explanations (though… Read More

TSMC OIP DAC Theater Schedule 2018

The TSMC OIP DAC Theater schedule is finalized and ready to go. It kicks off Monday at 10:15 am in booth #1629 and ends with a raffle at 5:45 pm each day (Mon-Tue-Wed) TSMC gives out some very nice prizes so check in with the TSMC booth staff when you arrive. There are 66 coveted presentation spots representing the top ecosystem partners… Read More

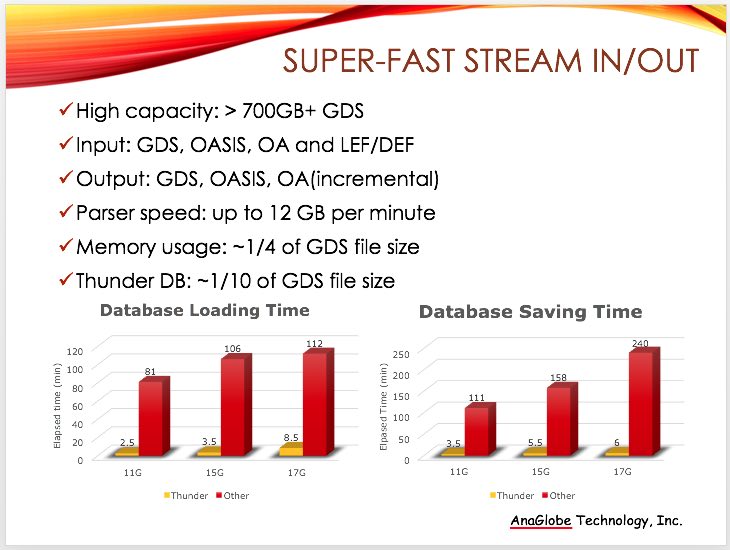

Billion Transistor Designs Need Faster Full Chip Tools

During the design cycle as tape out approaches, time pressure usually goes up dramatically. To make matters worse the design itself is much larger, because all the block level work is done and there is a requirement to work with the entire database. It feels like it’s time to put aside the garden trowel and start using a steam shovel.… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center