We have entered the age of AI specific processors, where specialized silicon is being produced to tackle the compute needs of AI. Whether they use GPUs, embedded programmable logic or specialized CPUs, many AI chips are based on parallel processing. This makes sense because of the parallel nature of AI computing. As a result, in… Read More

Carbon in the Age of AI Chips: What the Semiconductor Industry Needs to Know This Earth DayStephen Russell: Senior Technical Fellow, TechInsights Every April,…Read More

Carbon in the Age of AI Chips: What the Semiconductor Industry Needs to Know This Earth DayStephen Russell: Senior Technical Fellow, TechInsights Every April,…Read More How to Overcome the Advanced Node Physical Verification BottleneckIt is well-known that advanced semiconductor process technology…Read More

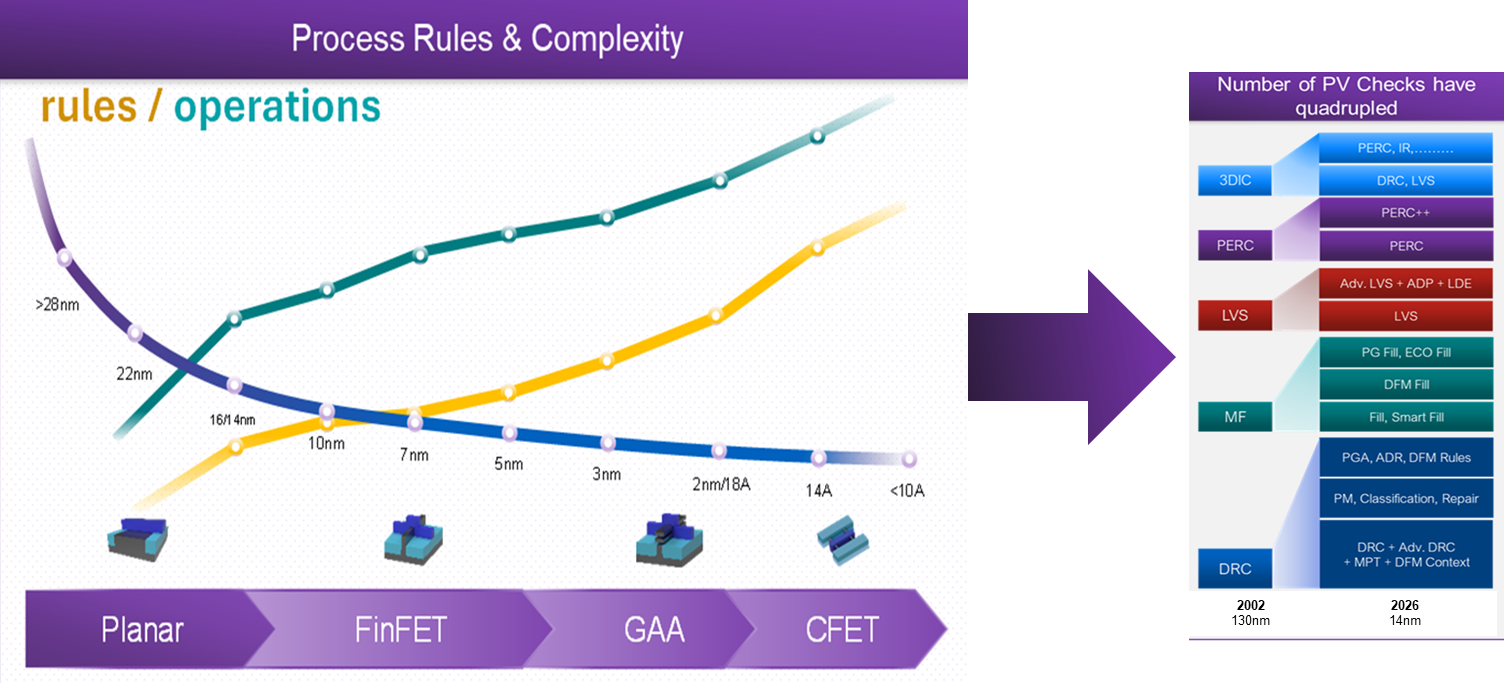

How to Overcome the Advanced Node Physical Verification BottleneckIt is well-known that advanced semiconductor process technology…Read More proteanTecs at Chiplet Summit – Changing the Game for Health & Performance Monitoring of ChipletsThe recent Chiplet Summit 2026 was a great…Read More

proteanTecs at Chiplet Summit – Changing the Game for Health & Performance Monitoring of ChipletsThe recent Chiplet Summit 2026 was a great…Read MoreSecretary Chao Unchained @ CES 2020

U.S. Department of Transportation Secretary Elaine Chao has agreed to mount the stage at the upcoming Consumer Electronics Show in Las Vegas to share her vision of the positive economic impact of technology unleashed from regulatory oversight. It’s a powerful message but it’s going to be a tough sell.

Chao is likely taking the… Read More

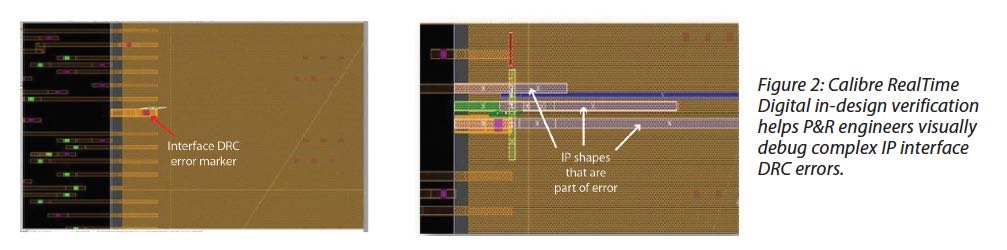

Qualcomm Attests Benefits of Mentor’s RealTime DRC for P&R

When floor planning (FP) and place & route (P&R) tools took over from custom layout tools for standard cell based designs, life became a lot better for designers of large digital chips. The beauty of the new flows was that all the internals of the standard cells and many IP blocks were hidden from view, lightening the load … Read More

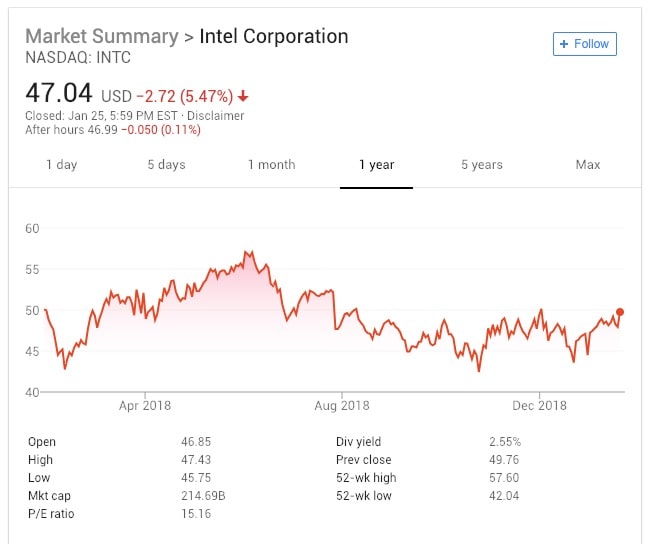

The 50th Year of Intel, What Happened in 2018

2018 was the 50th year for Intel in the semiconductor business, and their Q4 2018 conference call just happened last week, so I’ll get you all caught up on what they talked about. Bob Swan is the CFO and interim CEO, as the company continues to search for a new CEO after Brian K. was ousted for misconduct. Here’s a quick financial… Read More

Why High-End ML Hardware Goes Custom

In a hand-waving way it’s easy to answer why any hardware goes custom (ASIC): faster, lower power, more opportunity for differentiation, sometimes cost though price isn’t always a primary factor. But I wanted to do a bit better than hand-waving, especially because these ML hardware architectures can become pretty exotic, so … Read More

Switch Design Signoff with IC Validator

The surge of network traffic at the data centers has driven to an increase in network bandwidth, doubling every 12-15 months according to a study conducted on Google’s data centers. The primary drivers to this uptick include the proliferation of cloud computing, more distributed storage architecture, emerging applications… Read More

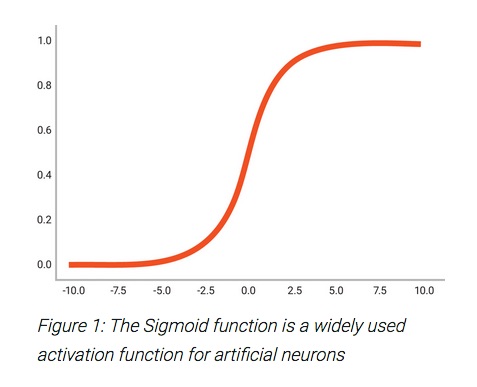

Mathematics are Hard – That is Why AI Needs Mathematics Hardware

The field of artificial intelligence has relied on heavy inspiration from the world of natural intelligence, such as the human mind, to build working systems that can learn and act on new information based on that learning. In natural networks, neurons do the work, deciding when to fire based on huge numbers of inputs. The relationship… Read More

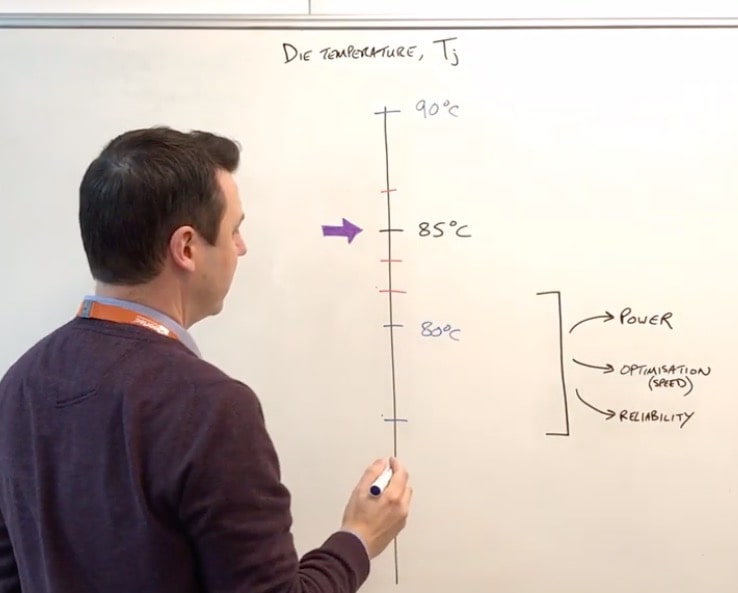

Accuracy of In-Chip Monitoring for Thermal Guard-banding

I remember working at Intel and viewing my first SPICE netlist for a DRAM chip, because there was this temperature statement with a number after it, so being a new college graduate I asked lots of questions, like, “What is that temperature value?”

My co-worker answered, “Oh, that’s the estimated junction… Read More

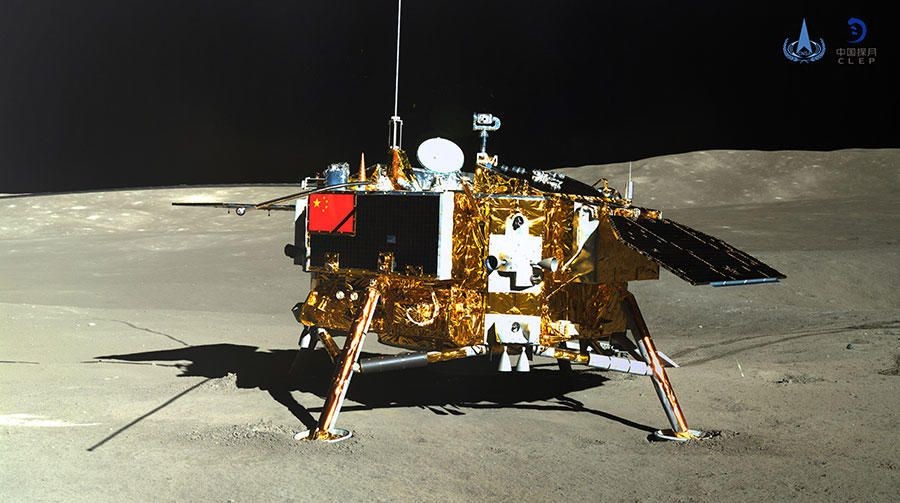

Why we will all benefit from the next space race

Until January 3, no human being had ever set eyes upon the “dark side” of the moon: the side always facing away from the Earth. It always remained a mystery. But no longer. China’s National Space Administration successfully landed a lunar lander, Chang’e-4, at South Pole-Aitken, the moon’s largest and deepest basin. Its lunar rover… Read More

ASML and Memory Loss 2019

ASML reported a more or less in line quarter as expected, coming in at EUR3.14B in revenues and EPS of EUR1.87. However, guidance was worse than most analysts were expecting with Q1 revenues expected to be EUR2.1B or down about one third.

This cut is something we have been talking about for a while as we have expected sharp memory CAPEX… Read More

Is Intel About to Take Flight?