DesignCon is coming up, kicking off the first of many industry conferences for the year. It’s at the Santa Clara Convention Center which is the best venue in Northern California. Not only is this a semiconductor crowd, it’s also a systems crowd covering chips, boards, and systems. More than 175 companies participate with an expected… Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More

Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read More

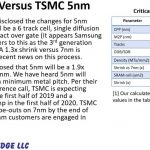

Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read MoreTSMC and Semiconductors 2019 and Beyond

TSMC has always been my bellwether and for 2019 I think we need to pay careful attention. Bad economic news has been spreading inside the fabless semiconductor ecosystem (tool and IP budgets have been tightening) but I think it is a bit premature. Let’s take a look at the TSMC 2018 Q4 earnings call and talk more about it in the comments… Read More

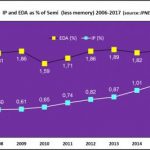

DAC 2019 Will Be Even More IP Friendly!

DAC 2019 will take place in Las Vegas (June 2-6) this year before moving back to San Francisco in 2020 and for the next 5 years. Considering the various rumors about merging the conference, or even the end of DAC, this is a very good news! Not only for Design Automation, but, as we will see, for the IP industry.

In fact, if we look at the exhibitor… Read More

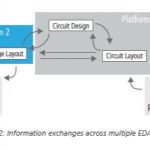

At Last, Package and Chip integration for RF Design

It seems that it has always been that there were packages and ICs, and in the design tool world “never the twain shall meet”. The tools for designing packages were completely separate from the tools used to design IC’s. This was so profoundly true that even after Cadence merged with Valid Logic back in the early 90’s, their Allegro … Read More

TSMC and Apple Aftermath

TSMC reported an in line quarter, as expected and also reported down Q1 guidance, also as expected. The only thing some investors may have been caught off guard about is the magnitude of the expected drop, 14%, from $9.4B to $7.35B. This is the largest quarter over quarter drop for TSMC in a very long time. Importantly for TSMC, 7NM … Read More

Remote Control: Crazy Likes Company

Three years ago Chris Valasek and Charlie Miller hacked an FCA Jeep to demonstrate the ability to remotely control a vehicle. The stunt was intended to make the point that the automotive industry had a problem with cybersecurity and the consequences of failing to deal with this vulnerability could be catastrophic.

As 2019 arrives,… Read More

CNBC Qualcomm and SemiWiki

Over the holidays I did an interview with CNBC on the subject of Qualcomm. The producer had read the History of Qualcomm chapter in our book Mobile Unleashed and wanted to base a 15 minute report on it. The interview lasted 90 minutes but of course only snippets of what I said were used. You can see the recorded report by clicking on the… Read More

Needham Growth Conference Notes 2019

We attended the Needham Growth Conference which is one of the first conferences of the year and in the quiet period before most companies reported so even though there was no “official” comment from most companies on the quarter, the surrounding commentary spoke volumes:

- The down cycle (and everyone admits its a cycle

The New Intel CEO

Interestingly, in some circles I’m known as an “Intel basher” but nothing could be further from the truth. I grew up with Intel and give them full credit for bringing serious compute power to our desktops. My first Intel powered computer was an IBM XT and I have had dozens of Intel based desktops and laptops since then. As a result, I … Read More

A Sharper Front-End to Intelligent Vision

In all the enthusiasm around machine learning (ML) and intelligent vision, we tend to forget the front-end of this process. The image captured on a CCD camera goes through some very sophisticated image processing before ML even gets to work on it. The devices/IPs that do this are called image signal processors (ISPs). You might … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center