Machine learning (ML) is already making its way into EDA tools and flows, but the majority of announcements have been around implementation, especially in guiding toward improved timing and area. This is a pretty obvious place to start; ML is in one sense an optimization technique, trained on prior examples, which should be able… Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More

WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More

WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read More

Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read More56th DAC Empyrean Stepping Up ALPS with GPU Implementation

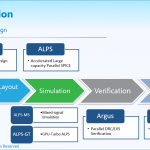

As a testament to the technology advances developed and implemented into Empyrean ALPS™ by the engineering team, the product has seen a steady growth in the adoption by users. In addition, hearing directly from the users at DAC 2018 turned out to be an all-around success for the product as well as the product team to see ALPS beating… Read More

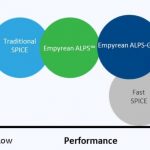

The Changing Landscape for SPICE Circuit Simulators

I first started using a SPICE circuit simulator in 1978 while at Intel and have followed that market ever since then. Back at DAC in 2012 I first heard of a Chinese EDA company called IC Scape with a SPICE circuit simulator called Aeolus, so I blogged about it. Fast forward to 2019 and I heard from Ravi Ravikumar, a former co-worker from… Read More

Semiconductor IP Security Issues

Every morning I read the headlines from SemiWiki, CNN, LinkedIn and my Twitter feed, and it seems like every week that I read about another security breach that makes me wonder if anything online is secure. Companies try to harden their web sites, IT infrastructure and even their electronic products from being exploited or tampered… Read More

Automotive Design and Virtual Prototyping

The entire history of EDA software tools has enabled engineers to design ICs and SoCs using virtual prototyping, so most of us in the industry are familiar with the idea of modeling and simulating something as complex as an IC before actually starting the manufacturing process. In a complex system like an automobile there are a lot… Read More

Silvaco Samsung and Excitement at 56thDAC

There were quite a few announcements at the Samsung Foundry Forum but my favorite was the IP partnership between Samsung and Silvaco. IP is a critical part of the fabless ecosystem and one of the advantages an IDM foundry has over a pure-play is the vast amounts of internal IP that have been silicon proven over the years. With Samsung… Read More

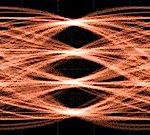

Monday DAC IP Session “PAM 4 Enable 112G SerDes”

This session will open the DAC IP Track at 10:30 on Monday “How PAM4 and DSP Enable 112G SerDes Design” in Room N264. I am very proud to chair this invited paper session, as it addresses one of the key pieces of design, enabling to exchange data flow at the highest possible data rate. It can be between two chips on the same board, we talk … Read More

400G Ethernet test chip tapes-out at 7nm from eSilicon

Since the beginning of May eSilicon has announced the tape-out of three TSMC 7nm test chips. The first of these, a 7nm 400G Ethernet Gearbox/Retimer design, caught my eye and I followed up with Hugh Durdan, their vice president of strategy and products, to learn more about it. Rather than just respin their 56G SerDes, they decided… Read More

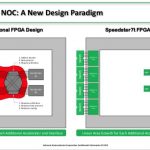

An evolution in FPGAs

Why does it seem like current FPGA devices work very much like the original telephone systems with exchanges where workers connected calls using cords and plugs? Achronix thinks it is now time to jettison Switch Blocks and adopt a new approach. Their motivation is to improve the suitability of FPGAs to machine learning applications,… Read More

Mentor Excitement at 56thDAC!

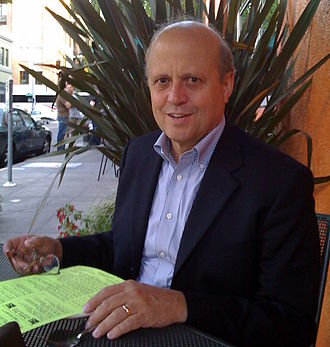

Mentor continues to invest in conferences such as DAC, no matter the location, for which I am very grateful. They have a long list of activities this year but I wanted to point out my top three:

Wally Rhines has a talk in the DAC Pavilion which is first on the list. Wally’s expert industry perspective is the result of tireless research… Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry