You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

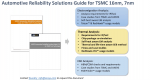

Semiconductors continue to surge and lead technology sectors all over the world. TSMC has always been my economic bellwether and 2019 was another great year as the TSM share price almost doubled. But it looks like the best is yet to come with TSMC significantly increasing CAPEX to cover 7nm and 5nm demand.

TSMC CEO C.C. Wei increased… Read More

In the past, I’ve focused my annual predictions on electronics – ICs and EDA – but recently I’ve turned my focus to photonics, so my 2020 predictions are primarily in this area.

Historically, photonics has been the Gallium Arsenide of technologies; it was, is and always will be the technology of the future. Analysts have forever … Read More

IEDM 2019 had the theme: “Innovative Devices for an Era of Connected Intelligence” of which MRAM is a leading contributor. Following a very informative Plenary Session, Monday afternoon led off with Session 2: Memory Technology – STT-MRAM. This session has seven important STT-MRAM papers describing the progress of this … Read More

My Lyft driver in San Jose thought his Hyundai had “autopilot,” alluding I suspected, to Tesla Motors’ feature of the same name which has placed that company at the forefront of driving automation development and the focal point of fatal crash investigations. Before either of us got hurt I gently disabused my driver of his dangerous… Read More

Over the last 40 years, Bernard has worked with semiconductor and EDA companies in hands-on, management and consulting roles in engineering, sales and marketing. He most recently co-founded Atrenta where he created and led the development of SpyGlass, retiring as CTO when Atrenta was acquired by Synopsys. Post-retirement,… Read More

Advanced IC technologies, 5nm and 7nm FinFET design and stacked packaging, are enabling massive levels of integration of super-fast circuits. These in turn enable much of the exciting new technology we hear so much about: mobile gaming and ultra-high definition mobile video through enhanced mobile broadband in 5G, which requires… Read More

It’s clear that blockchain will revolutionize operations and processes in many industries and governments agencies if adopted, but its adoption requires time and efforts, in addition blockchain technology will stimulate people to acquire new skills, and traditional business will have to completely reconsider their processes… Read More

The media is trying to disparage the semiconductor industry again. It’s hard to not take this type of desperate journalism personal. Semiconductor people are the smartest and hardest working people in the world and we deserve better, absolutely.

TSMC founder sees trade dispute as ‘reality show with no script’… Read More

When I landed at San Francisco International Airport last Tuesday morning around 1 a.m. I was determined to locate the airport taxi rank and take a cab to my hotel in Santa Clara. The idea of hailing an Uber or Lyft seemed essentially nonsensical to me since I knew professional taxi drivers would be waiting as they usually are at most… Read More

I recently wrote about this year’s Cadence Photonics Summit. As I mentioned in that post, it was a fascinating event with several companies providing useful and informative presentations. You can access some of the presentations on the event site. One presentation, given by Jose Capmany of iPronics, was especially interesting… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center