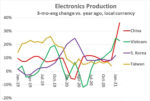

Electronics production has recovered strongly from slowdowns due to the COVID-19 pandemic. Most major Asian electronic producers reported double-digit increases in early 2021. The chart below shows three-month-average change versus a year ago for electronics production. The data is from each country’s official statistics… Read More

Podcast EP12: A Close Look at Intel with Stacy Rasgon

Dan takes an in-depth look at Intel with Stacy Rasgon, Managing Director and Senior Analyst, U.S. Semiconductors at Bernstein Research. Stacy is an unusual semiconductor analyst as he holds a Ph.D. in chemical engineering from MIT. His substantial technical knowledge allows for a deep dive on Intel that you will find refreshing… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center