Akeana Inc. announced a key milestone in the development of its advanced RISC-V technology: a successful partnership with Axiomise Limited to formally verify its super-scalar test chip, Alpine. The collaboration highlights the growing importance of formal verification in ensuring correctness, performance, and efficiency

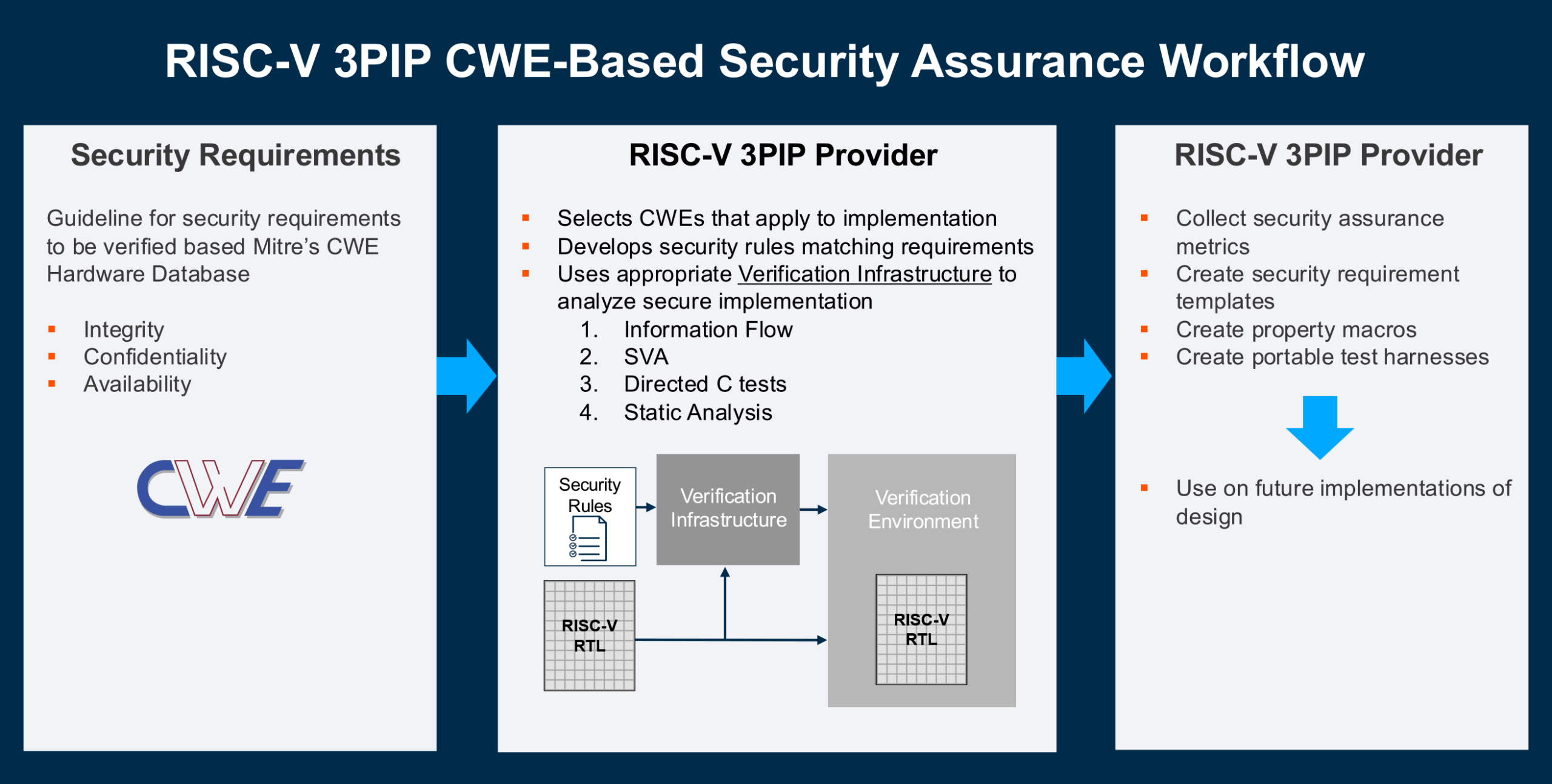

Securing RISC-V Third-Party IP: Enabling Comprehensive CWE-Based Assurance Across the Design Supply Chainby Jagadish Nayak RISC-V adoption continues to accelerate…Read More

Securing RISC-V Third-Party IP: Enabling Comprehensive CWE-Based Assurance Across the Design Supply Chainby Jagadish Nayak RISC-V adoption continues to accelerate…Read More Apple’s iPhone 17 Series 5G mmWave Antenna Module Revealed to be Powered by Soitec FD-SOI SubstratesRecent independent teardown and technical analyses have confirmed…Read More

Apple’s iPhone 17 Series 5G mmWave Antenna Module Revealed to be Powered by Soitec FD-SOI SubstratesRecent independent teardown and technical analyses have confirmed…Read More Advancing Automotive Memory: Development of an 8nm 128Mb Embedded STT-MRAM with Sub-ppm Reliability IEDM 2025 Papers MRAM…Read More

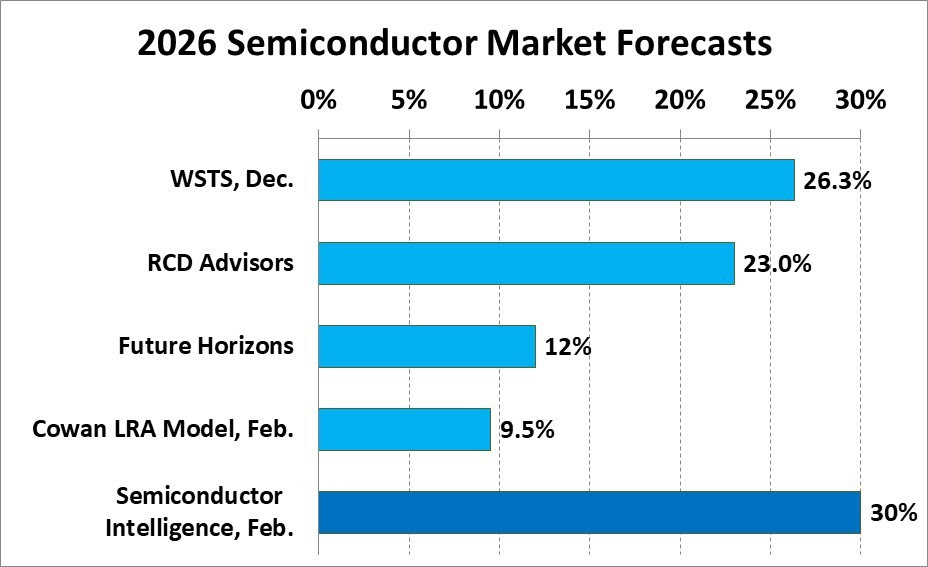

Advancing Automotive Memory: Development of an 8nm 128Mb Embedded STT-MRAM with Sub-ppm Reliability IEDM 2025 Papers MRAM…Read More AI Drives Strong Semiconductor Market in 2025-2026The global semiconductor market in 2025 was $792…Read More

AI Drives Strong Semiconductor Market in 2025-2026The global semiconductor market in 2025 was $792…Read More How Customized Foundation IP Is Redefining Power Efficiency and Semiconductor ROIAs computing expands from data centers to edge…Read More

How Customized Foundation IP Is Redefining Power Efficiency and Semiconductor ROIAs computing expands from data centers to edge…Read MoreAn AI-Native Architecture That Eliminates GPU Inefficiencies

A recent analysis highlighted by MIT Technology Review puts the energy cost of generative AI into stark perspective. Generating a simple text response from Llama 3.1-405B—a model with 405 billion parameters, the adjustable “knobs” that enable prediction—requires on average 3,353 joules, nearly 1 watt-hour (Wh). Once cooling… Read More

Caspia Technologies Unveils A Breakthrough in RTL Security Verification Paving the Way for Agentic Silicon Security

In a significant advancement for the semiconductor industry, Caspia Technologies announced the broad availability of CODAx V2026.1, its flagship RTL security analyzer. The new release strengthens early-stage hardware security verification and positions the company to deliver fully agentic workflows that automate vulnerability… Read More

Designing the Future: AI-Driven Multi-Die Innovation in the Era of Agentic Engineering

At the 2026 Chiplet Summit, Synopsys presented a bold vision for the future of semiconductor innovation: AI-driven multi-die design powered by agentic intelligence. As the semiconductor industry shifts rapidly toward chiplet-based architectures and 3D stacking, the complexity of design, verification, and system integration… Read More

An Agentic Formal Verifier. Innovation in Verification

In a break from our academic-centric picks, here we look at an agentic verification flow developed within a semiconductor company. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and lecturer at Stanford, EE292A) and I continue our series on research ideas.… Read More

Reimagining Compute in the Age of Dispersed Intelligence

At the 2025 RISC-V Summit, amid debates over cloud scaling and AI cost, DeepComputing CEO Yuning Liang offered a radical view: the future of intelligence isn’t in the cloud at all — it’s already in your pocket. His lunchtime conversation began with iPhones and ended with the death of the operating system. In between, he sketched … Read More

Siemens to Deliver Industry-Leading PCB Test Engineering Solutions

Siemens has strengthened its position in EDA and manufacturing by acquiring ASTER Technologies, a specialist in test and reliability solutions for printed circuit boards. The acquisition represents a strategic step in Siemens’ broader vision to deliver a fully integrated, end-to-end digital thread for electronics design,… Read More

Agentic EDA Panel Review Suggests Promise and Near-Term Guidance

NetApp recently hosted a webinar on Agentic AI as the future for EDA and implications for infrastructure. Good list of panelists including Mahesh Turaga (VP Cadence Cloud) with an intro preso on infrastructure and agentic AI at Cadence, then our own Dan Nenni (Mr. SemiWiki) moderating, Khaled Heloue (Fellow AMD, CAD CAD/Methodology/AI),… Read More

Hardware is the Center of the Universe (Again)

The 40-Year Evolution of Hardware-Assisted Verification — From In-Circuit Emulation to AI-Era Full-Stack Validation

For more than a decade, Hardware-Assisted Verification platforms have been the centerpiece of the verification toolbox. Today, no serious semiconductor program reaches tapeout without emulation or FPGA-prototyping… Read More

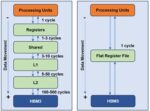

An AI-Native Architecture That Eliminates GPU Inefficiencies