The adoption of 3DIC architectures, while not new, is enjoying a surge in popularity as product developers look to their inherent advantages in performance, cost, and the ability to combine heterogeneous technologies and nodes into a single package. As designers struggle to find ways to scale with complexity and density limitations… Read More

The Great Divide: A Tale of Three Hardware Emulation ArchitecturesHardware emulation arose as a necessity out of…Read More

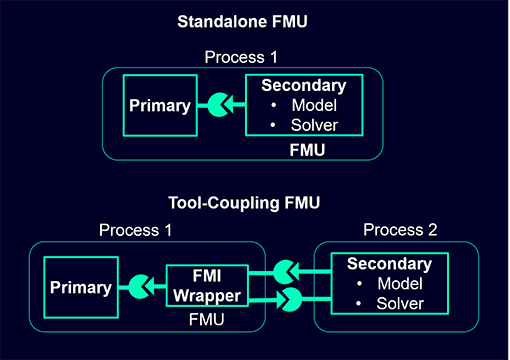

The Great Divide: A Tale of Three Hardware Emulation ArchitecturesHardware emulation arose as a necessity out of…Read More A Different Angle on Co-Simulation for SystemsCo-simulation, two or more simulations running concurrently in…Read More

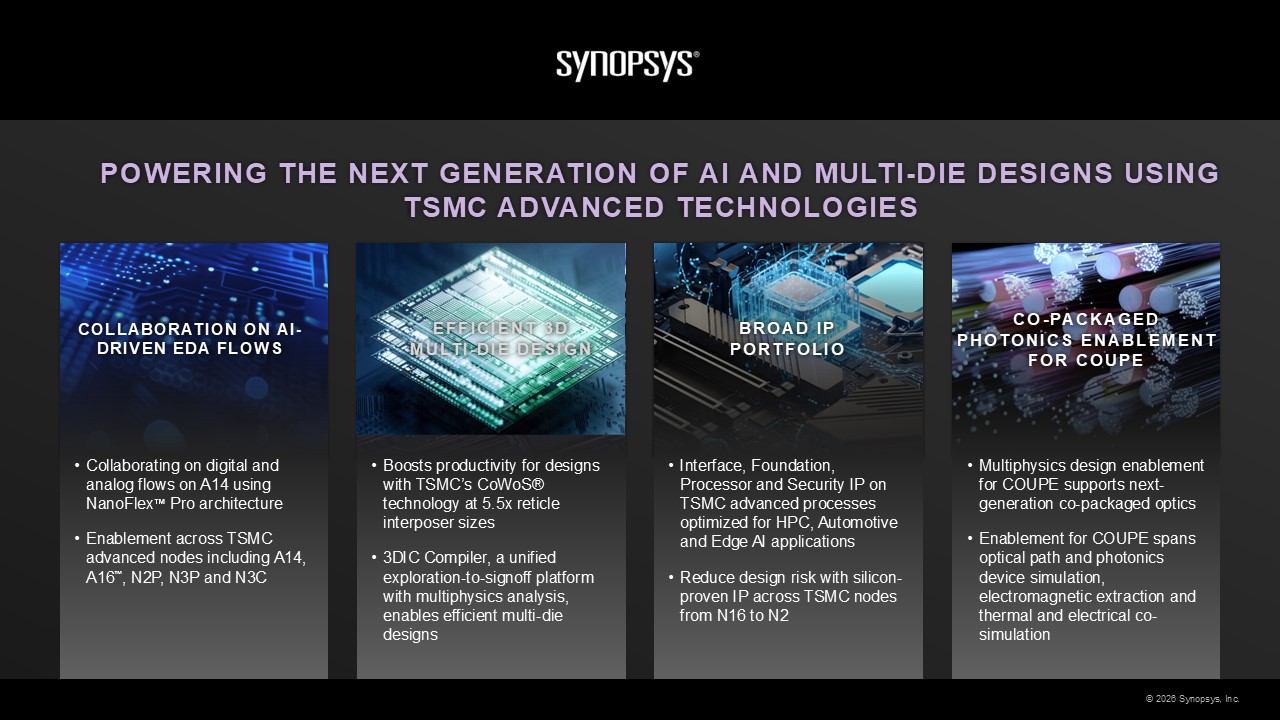

A Different Angle on Co-Simulation for SystemsCo-simulation, two or more simulations running concurrently in…Read More Synopsys and TSMC Deepen AI Design Alliance: What It MeansA recent announcement from Synopsys signals a meaningful…Read More

Synopsys and TSMC Deepen AI Design Alliance: What It MeansA recent announcement from Synopsys signals a meaningful…Read MoreOptimize AI Chips with Embedded Analytics

The foundry model, multi-source IP blocks, advanced packaging technologies, cloud computing, hyper-connectivity and access to open-source software have all contributed to the incredible electronics products of recent times. Along with this, the complexity of developing and taking a chip to market has also increased. And… Read More

Intel Architecture Day – Part 2: GPUs, IPUs, XeSS, OpenAPI

Introduction

At the recent Intel Architecture Day presentations, a breadth of roadmap plans were provided – an earlier article focused on the x86 client and data center cores and products. This article focuses on the GPU and IPU announcements.

Xe Graphics Core

The Intel GPU architecture for embedded, discrete, and data center… Read More

Intel Architecture Day – Part 1: CPUs

Introduction

The optimization of computing throughput, data security, power efficiency, and total cost of ownership is an effort that involves managing interdependencies between silicon and packaging technologies, architecture, and software. We often tend to focus on the technology, yet the architecture and software… Read More

AMS IC Designers need Full Tool Flows

Digital IC design gets a lot of attention, because all of our modern devices primarily use digital logic, but in reality whenever you have a sensor like a camera, accelerometer, gyroscope or any radio like Bluetooth, WiFi or NFC, then you’re really in the realm of analog, and that’s where mixed-signal IC design comes… Read More

Smoothing the Path to NoC Adoption

We’re creatures of habit. As technologists, we want to move fast and break things, but only on our terms. Everything else should remain the same or improve with minimum disruption. No fair breaking the way we do our jobs as we plot a path to greatness. This is irrational, of course. Real progress often demands essential changes where… Read More

Webinar – Why Keeping Track of IP in the Enterprise Really Matters

Everyone knows IP is an important asset for the enterprise. You spend a lot of money on IP licenses. You try to keep track of who bought what as buying the same thing twice is painful. You wonder if you have the latest version of an IP, especially if it’s part of mission-critical functionality. If you’re a good corporate citizen, you … Read More

NetApp’s ONTAP Enables Engineering Productivity Boost

One of the few things that remain constant in the engineering world is the desire for higher productivity. Innovation happens when engineers are designing something and creative ideas crop up when they are reviewing and analyzing the results. In between these fun steps, engineers have to deal with the necessary evil of creating… Read More

GM Fires First 5G Shot

Connecting cars remains one of the most unnatural acts in the world of IoT. “Connected Car” headlines might make you think otherwise, but the reality is that precious few cars on the road today are connected with a live, provisioned and functioning wireless connection. That being said, General Motors claims 16M of those cars

Accelerating Exhaustive and Complete Verification of RISC-V Processors

As processor architecture and design development becomes completely liberated with open-source RISC-V instruction set architecture (ISA), the race to get RISC-V silicon in our hands has increased massively. We have no doubt that in next 5 years, we will see RISC-V based laptops and desktops in the market. But would these processors… Read More

Siemens U2U 3D IC Design and Verification Panel