SemiWiki has covered the Q2, Q3 and Q4 ESD Alliance quarterly revenue reports previously. The Q2 2020 report suggested that EDA had COVID immunity. The Q3 2020 report inspired an Up and to the Right comment. The Q4 2020 report demanded a Juggernaut label. And now the Q1 2021 report posts yet more record-breaking growth. This is … Read More

Scaling Multi-Die Connectivity: Automated Routing for High-Speed InterfacesThis article concludes the three-part series examining key…Read More

Scaling Multi-Die Connectivity: Automated Routing for High-Speed InterfacesThis article concludes the three-part series examining key…Read More Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More

WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More

WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read MoreFully Modeling the Semiconductor Manufacturing Process

A lot of folks in the semiconductor business are familiar with Dassault Systèmes because of their product life cycle management (PLM) products for IC design. They are, of course well known in other industries as well for their 3D modeling and simulation software. Over the years they have added capabilities and intelligence to … Read More

Get a Jump-Start on Your Next IoT Design with Sondrel’s SFA 100

The concept of platform-based design has been around a long time. I can recall Nokia’s early cell phone products used the strategy very effectively. They were able to turn out new phones quickly by leveraging their existing chip design as a baseline on which to add features. This is commonplace today but was innovative at that time.… Read More

StarFive Surpasses Development Goal with the Prodigy Rapid Prototyping System from S2C

Faced with the challenge of developing a high-performance hardware platform with critical software components, what choices do companies have in rapidly moving their development forward with modest budgets and resources?

That was the challenge faced by StarFive Technology, a leading IP and semiconductor SoC platform solution… Read More

Obtaining Early Analog Block Area Estimates

I’ve written before about Pulsic’s Animate Preview software, which is extremely helpful in completing placement in analog blocks so that they are ready for routing. Analog design automation has always been a tough proposition, but Animate Preview looks like a promising tool, with practical benefits. Obtaining DRC clean placement… Read More

Automotive Safety Island: Test, Safety, Security, ISO 26262

I first fell in love with electric vehicles back in 1978 as an Electrical Engineering student, studying at the University of Minnesota. What caught my fancy was a small advertisement listed in the back of Popular Mechanics magazine to build your own electric vehicle by replacing the gas engine of a Honda with an electric motor, so… Read More

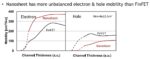

TSMC Design Considerations for Gate-All-Around (GAA) Technology

The annual VLSI Symposium provides unique insights into R&D innovations in both circuits and technology. Indeed, the papers presented are divided into two main tracks – Circuits and Technology. In addition, the symposium offers workshops, forums, and short courses, providing a breadth of additional information.

At… Read More

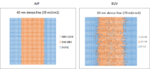

Stochastic Origins of EUV Feature Edge Roughness

Due to the higher energy of EUV (13.3-13.7 nm wavelength) compared to ArF (193 nm wavelength) light, images produced by EUV are more susceptible to photon shot noise.

Figure 1. (Left) 40 nm dense (half-pitch) line image projected onto wafer at 35 mJ/cm2; (Right) 20 nm dense (half-pitch) line image projected onto wafer at 70 mJ/cm2.… Read More

Apple’s Orphan Silicon

Apple’s recent Spring Loaded Event brought us M1-based iMacs. After the MacBook Air and 13” MacBook Pro in the fall, iMacs are the third Mac to jettison Intel processors. With this transition Apple’s T2 chip enters End of Life status, so to speak. The T2 is a bit of an enigma and now it does not have much time left.

We know it performs… Read More

Podcast EP28: Funding approaches for semiconductor startups

Dan is joined by Wally Rhines to discuss funding approaches for semiconductor startups. Wally has led a fundraising effort for a fabless semiconductor startup for the last year. His experience is useful for others who are trying to raise funding for promising semiconductor startups.

Wally Rhines is widely recognized as an expert

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era