I recently had an eye-opening discussion regarding the phenomena of soft errors in semiconductor devices. I always knew this could be a problem in space, where there are all kinds of high energy particles. What I didn’t realize is there are two trends that are making this kind of problem relevant on the ground as well as in space. The… Read More

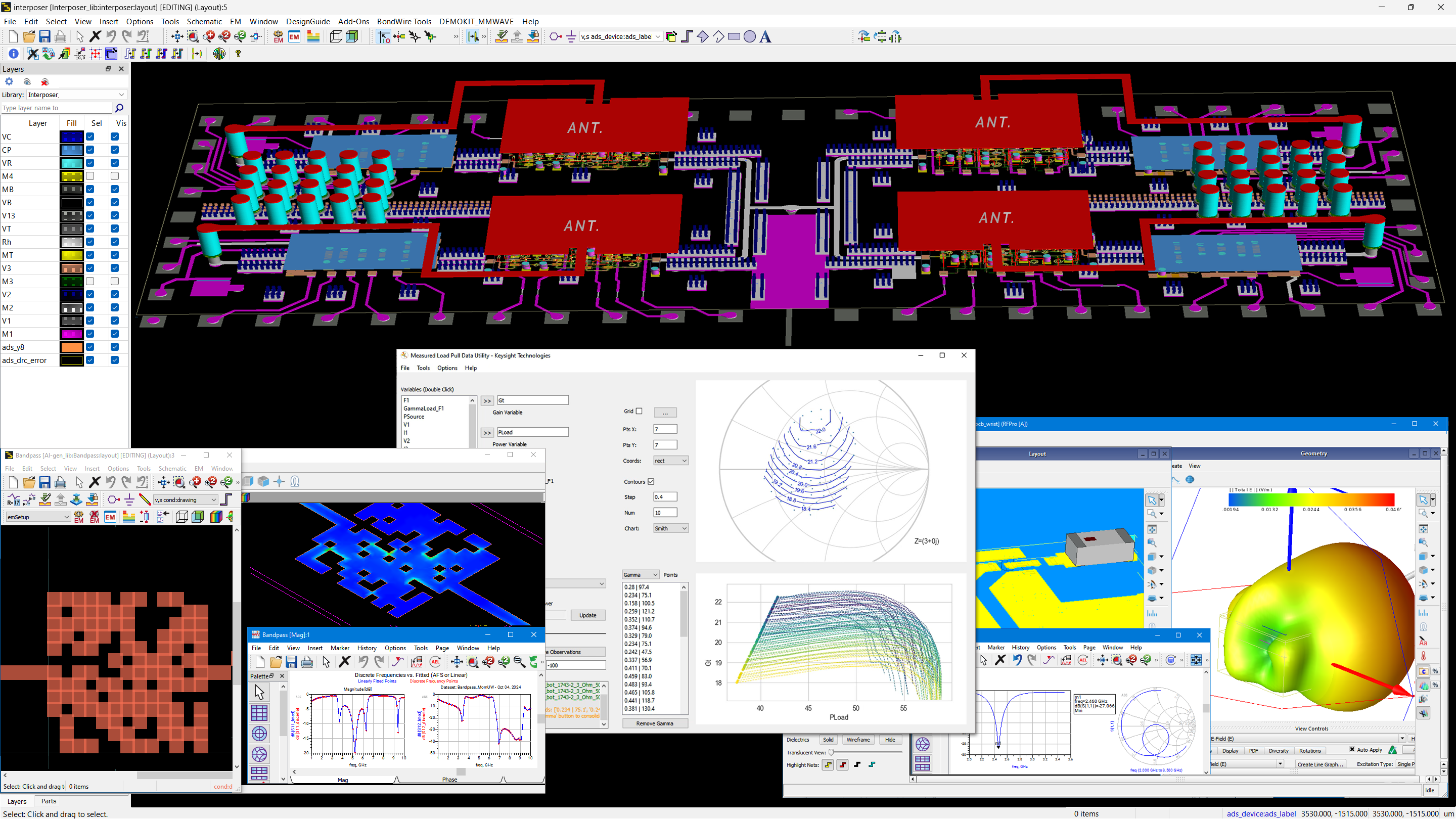

Keysight EDA 2025 launches AI-enhanced design workflowsThe upcoming Keysight EDA 2025 launch has three…Read More

Keysight EDA 2025 launches AI-enhanced design workflowsThe upcoming Keysight EDA 2025 launch has three…Read More Changing RISC-V Verification Requirements, Standardization, InfrastructureA lively panel discussion about RISC-V and open-source…Read More

Changing RISC-V Verification Requirements, Standardization, InfrastructureA lively panel discussion about RISC-V and open-source…Read More Semidynamics: A Single-Software-Stack, Configurable and Customizable RISC-V SolutionFounded with a vision to create transformative, customizable…Read More

Semidynamics: A Single-Software-Stack, Configurable and Customizable RISC-V SolutionFounded with a vision to create transformative, customizable…Read More Synopsys-Ansys 2.5D/3D Multi-Die Design Update: Learning from the Early AdoptersThe demand for high-performance computing (HPC), data centers,…Read More

Synopsys-Ansys 2.5D/3D Multi-Die Design Update: Learning from the Early AdoptersThe demand for high-performance computing (HPC), data centers,…Read More Arteris Empowering Advances in Inference AcceleratorsSystolic arrays, with their ability to highly parallelize…Read More

Arteris Empowering Advances in Inference AcceleratorsSystolic arrays, with their ability to highly parallelize…Read MoreDriving Data Frontiers: High-Performance PCIe® and CXL® in Modern Infrastructures

The increasing demands of data-intensive applications necessitate more efficient storage and memory utilization. The rapid evolution of AI workloads, particularly with Generative AI (GenAI), demands infrastructure that can adapt to diverse computational needs. AI models vary widely in resource requirements, necessitating… Read More

TSMC Advanced Packaging Overcomes the Complexities of Multi-Die Design

The TSMC Technology Symposium provides a worldwide stage for TSMC to showcase its advanced technology impact and the extensive ecosystem that is part of the company’s vast reach. These events occur around the world and the schedule is winding down. TSMC covers many topics at its Technology Symposium, including industry-leading… Read More

Blank Wafer Suppliers are not Totally Blank

AI requires more Silicon capacity

Deep in the supply chain, some wizards turn sand into perfect diamond-structured crystal disks of silicon, which are necessary for the entire semiconductor supply chain.

They are part of the semiconductor supply chain, making Silicon Sand almost a thousand times more valuable.

The glimmer … Read More

Podcast EP227: The Significance of the RISC-V Movement and the Upcoming Andes RISC-V event with Mark Himelstein

Dan is joined by Mark Himelstein, President of Heavenstone. Most recently, as Chief Technology Officer at RISC-V International, Mark contributed to shaping RISC-V technology through visionary leadership and industry expertise. He has a track record of executive roles at Graphite Systems, Quantum, and Infoblox.

Dan discusses… Read More

Accelerate SoC Design: Addressing Modern Prototyping Challenges with S2C’s Comprehensive Solutions (II)

In the fast-paced world of Electronic Design Automation (EDA), the complexity of chip designs is continuously rising. With the burgeoning of systems such as 5G communication devices and Advanced Driver-Assistance Systems (ADAS) teeming with thousands of components, the demand for robust and efficient prototyping platforms… Read More

CEO Interview: Dieter Therssen of Sigasi

Dieter Therssen obtained his master’s degree in Electronics Engineering from KU Leuven in 1987. He started his career as a hardware design engineer, using IMEC’s visionary tools and design methodologies in the early days of silicon integration.

Since then, Dieter developed his career across many digital technologies,… Read More

3DIC Verification Methodologies for Advanced Semiconductor ICs

At the recent User2user conference, Amit Kumar, Principal Hardware Engineer, Microsoft, shared the company’s experience from building a 3DIC SoC and highlighted Siemens EDA tools that were used. The following is a synthesis of core aspects of that talk.

3DIC Challenges

Despite the numerous advantages of 3DIC technology, its… Read More

Mastering Copper TSV Fill Part 3 of 3

Establishing void-free fill of high aspect ratio TSVs, capped by a thin and uniform bulk layer optimized for removal by CMP, means fully optimizing each of a series of critical phases. As we will see in this 3-part series, the conditions governing outcomes for each phase vary greatly, and the complexity of interacting factors means… Read More

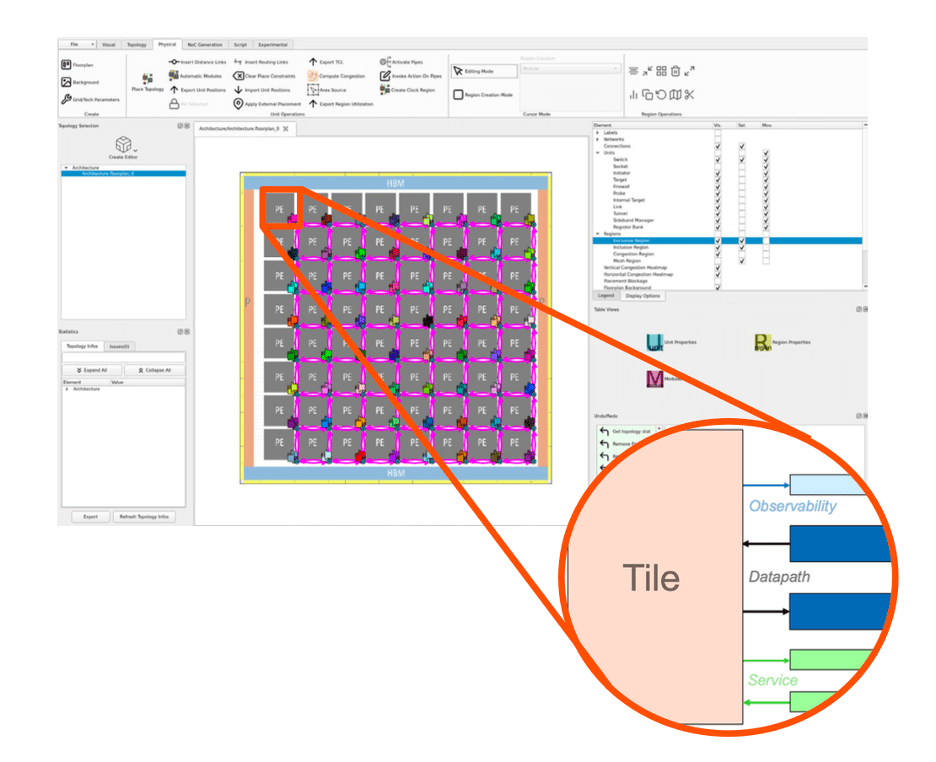

Arteris is Solving SoC Integration Challenges

The difficulty of SoC integration is clearly getting more demanding. Driven by process node density, multi-chip integration and seemingly never-ending demands for more performance at lower power, the hurdles continue to increase. When you consider these challenges in the context of Arteris, it’s natural to think about hardware… Read More

Build a 100% Python-based Design environment for Large SoC Designs