As the market for edge processing is growing, the performance, power and cost requirements of these applications are getting increasingly demanding. These applications have to work on instant data and make decisions in real time at the user end. The applications span the consumer, commercial and industrial market segments.… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data CenterAt the TERAFAB launch event in Austin on…Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data CenterAt the TERAFAB launch event in Austin on…Read More Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More

Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read MoreSemiconductor Decline in 2023

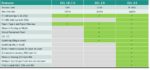

The semiconductor market dropped 0.8 percent in 2Q 2022 versus 1Q 2022, according to WSTS. The 2Q 2022 decline followed a 0.5% quarter-to-quarter decline in 1Q 2022. The 2Q 2022 revenues of the top 15 semiconductor suppliers match the overall market results, with a 1% decline from 1Q 2022. The results by company were mixed. Memory… Read More

Load-Managing Verification Hardware Acceleration in the Cloud

There’s a reason the verification hardware accelerator business is growing so impressively. Modern SoCs – now routinely multi-billion gate devices – must be verified/validated against massively demanding test plans, requiring high levels of test coverage. Use cases extend all the way up to firmware, OSes, even application… Read More

The Truly Terrifying Truth about Tesla

When I think about Tesla’s impact on the wider automotive industry, I conjure images of auto CEOs waking up in the middle of the night in cold sweats. It isn’t just that Tesla virtually or actually gets away with murder, it’s that the level of impunity is almost completely unchallenged by regulators and is actually celebrated by consumers… Read More

Die-to-Die Interconnects using Bunch of Wires (BoW)

Chiplets are a popular and trending topic in the semiconductor trade press, and I read about SoC disaggregation at shows like ISSCC, Hot Chips, DAC and others. Once an SoC is disaggregated, the next challenge is deciding on the die-to-die interconnect approach. The Open Compute Project (OCP) started 10 years ago as a way to share… Read More

Verification IP Hastens the Design of CXL 3.0

Although version 2.0 of the Computer Express Link (CXL) standard is just making it into new designs, the next generation, version 3.0, has been approved and is now ready for designers to implement the new silicon and firmware needed to meet the new standard’s performance specifications. CXL, an open industry-standard interconnect,… Read More

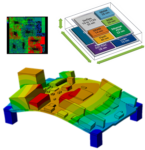

Ansys’ Emergence as a Tier 1 EDA Player— and What That Means for 3D-IC

Over its 40+ year history, electronic design automation (EDA) has seen many companies rise, fall, and merge. In the beginning, in the 1980s, the industry was dominated by what came to be known as the big three — Daisy Systems, Mentor Graphics, and Valid Logic (the infamous “DMV”). The Big 3 has morphed over the years, eventually settling… Read More

Finally, A Serious Attack on Debug Productivity

Verification technologies have progressed in almost all domains over the years. We’re now substantially more productive in creating tests for block, SoC and hybrid software/hardware verification. These tests provide better coverage through randomization and formal modeling. And verification engines are faster – substantially… Read More

WEBINAR: O-RAN Fronthaul Transport Security using MACsec

5G provides a range of improvements compared to existing 4G LTE mobile networks in regards to capacity, speed, latency and security. One of the main improvements is in the 5G RAN; it is based on a virtualized architecture where functions can be centralized close to the 5G core for economy or distributed as close to the edge as possible… Read More

Advanced EM simulations target conducted EMI and transients

A vital benefit of advanced EM simulations is their ability to take on complicated physical test setups, substituting far easier virtual tests yielding accurate results earlier during design activities. The latest release of Keysight PathWave ADS 2023 continues speeding up engineering workflows. Let’s look at three… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center