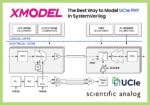

Join this webinar and see UCIe in action! This webinar presents the SystemVerilog models of a Universal Chiplet Interconnect Express (UCIe) interface, including both the analog circuits in the electrical layer and digital FSMs in the logical layer. The whole physical layer (PHY) model can be efficiently simulated in SystemVerilog,… Read More

Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read More

Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read More Scaling Multi-Die Connectivity: Automated Routing for High-Speed InterfacesThis article concludes the three-part series examining key…Read More

Scaling Multi-Die Connectivity: Automated Routing for High-Speed InterfacesThis article concludes the three-part series examining key…Read More Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read MorePodcast EP165: The Impact of Mobiveil Across the Industry with Ravi Thummarukudy

Dan is joined by Ravi Thummarukudy. Ravi is CEO of Mobiveil, a fast-growing supplier of silicon intellectual property (SIP), platforms and IP-enabled design services with designs deployed in millions of units of silicon embedded in communications and consumer products worldwide.

Dan explores the silicon IP products, platforms… Read More

A Primer on EUV Lithography

Extreme ultraviolet (EUV) lithography systems are the most advanced lithography systems in use today. This article is a basic primer on this important yet complex technology.

The Goal: A Smaller Wavelength

The introduction of 13.5 nm wavelength continues a trend the semiconductor industry had been following a wavelength reduction… Read More

WEBINAR: Driving Forward with UWB Radar: Enhancing Child Safety in Automotive

The rapid advancement of UWB (Ultra-Wideband) wireless technology has garnered significant attention and interest, thanks to its adoption by leading smartphone brands and its versatile range of applications. Within the automotive industry, UWB has already emerged as the preferred choice for Digital Keys in the premium… Read More

Real-Time AI-driven Image Signal Processing with Reduced Memory Footprint and Processing Latency

In our day to day lives, we all benefit from image signal processing (ISP), whether everyone realizes it or not. ISP is the technique of processing image data captured by an imaging device. It involves a series of algorithms that transform raw image data into a usable image by correcting for distortions, removing noise, adjusting… Read More

Investing in a sustainable semiconductor future: Materials Matter

In 2020 TSMC established its Net Zero Project with a goal of net zero emissions by 2050. I remember wondering how could this possibly be done before 2050 or at all for that matter. After working with TSMC for 20+ years I have learned never to bet against them on any topic and green manufacturing is one of them, absolutely.

TSMC presented… Read More

Coherent Optics: Synergistic for Telecom, DCI and Inter-Satellite Networks

The telecommunications industry has experienced significant growth in recent years, driven by the increasing demand for high-speed internet and data services. This growth has created a surge in traffic on optical networks, leading to the development of new telecom network architectures that can support the increasing demand… Read More

Deep Learning for Fault Localization. Innovation in Verification

A new look at fault localization and repair in debug using learning based on deep semantic features. Paul Cunningham (Senior VP/GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and now Silvaco CTO) and I continue our series on research ideas. As always, feedback welcome.

The

… Read MoreWEBINAR: An Ideal Neural Processing Engine for Always-sensing Deployments

Always-sensing cameras are a relatively new method for users to interact with their smartphones, home appliances, and other consumer devices. Like always-listening audio-based Siri and Alexa, always-sensing cameras enable a seamless, more natural user experience. However, always-sensing camera subsystems require specialized… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era