An earlier blog started with the topic of delivering 3D IC innovations faster. The blog covered the following foundational enablers for successful heterogeneous 3D IC implementation.

- System Co-Optimization (STCO) approach

- Transition from design-based to systems-based optimization

- Expanding the supply chain and tool ecosystem

- Balancing design resources across multiple domains

- Tighter integration of the various teams

The UCI-Express standard is driving the adoption of heterogeneous chiplets integration and with it the adoption of 3D IC implementations. When a new capability gets ready for mainstream, its mass adoption success depends on a number of things. While the foundational enablers are important, they are not sufficient for easily, quickly, effectively and efficiently delivering a successful solution. Standardized protocols are needed to offer plug-and-play compatibility between chiplet suppliers. With new requirements and signoffs, design tools evolve to meet and resolve any new challenges that arise. What the mainstream users need is a way to best use the tools to get an edge in the competitive marketplace. That boils down to key workflows which is the topic of a recent whitepaper published by Siemens EDA. This blog will cover the salient points from that whitepaper.

Workflow Adoption

There are two approaches to a chiplet based design. One approach uses a process of disaggregation wherein a complex monolithic chip is decomposed into plug-and-play modules to be assembled and interconnected with a silicon interposer. The other approach uses general purpose building block chiplets that are assembled and interconnected with an ASIC to build the system. Whichever approach is adopted, chiplet based designs add levels of complexity that must be understood and planned for.

The following five workflow adoption focus areas lend themselves to a managed methodology process that minimizes risk and cost and accelerates time to market benefit.

Early Planning and Predictive Analysis

Early planning and predictive analysis of the complete package assembly is mandatory with heterogeneous chiplets based systems. This involves thermal and power delivery considerations, chiplet co-optimization, chiplet interface management and design.

Chiplets often introduce new connectivity structures such as 3D stacking, TSVs, bumps, hybrid bonding and copper pillars. These structures can cause thermal induced stresses leading to performance and reliability problems. Investigating the connectivity structures for available alternate material options can help prevent unexpected failures that require late stage design changes.

Predictive power delivery analysis should be performed early in the process. Even though it may be approximate, this analysis averts later stage layout issues. A typical approach is to approximate the percentage of metal coverage per routing layer using Monte Carlo type sweep analysis. This analysis helps identify and communicate to the layout team, the parts of the circuit that would have the greatest impact on performance.

Waiting until the chiplet bump array is fully defined will delay package planning and limit the ability for co-optimization. The package planning can begin even before the chiplet design has started. The chiplet’s bump array and signal assignments can be created at the interposer level and passed to the IC design team for iterating, as the design progresses.

Standardized interfaces and protocols are key for broad adoption of chiplets based designs. At the same time, describing these interfaces brings new challenges for designers. Current approaches such as schematic description or HDL coding introduce the risk of human introduced errors. To overcome this challenge, Siemens EDA has developed a new approach called interface-based design that lends itself to automation.

Automating Interface-Based Design

Interface based design (IBD) is a new approach to capturing, designing, and managing large numbers of complex interfaces that interconnect multiple chiplets. With an interface defined as an IBD object, the designer can focus on a higher level of connectivity abstraction. The interface description becomes part of the chiplet part model. When a designer places an instance of this chiplet, everything related to the interface is automatically put in place. This approach allows designers to explore, define, and visualize route planning without having to transition the design into a substrate place-and-route tool. It enables more insightful chiplet floorplanning and chiplet-to-package or chiplet- to-interposer signal assignments. The IBD methodology helps establish correct-by-design chiplet connectivity.

Thermal, Stress and Reliability Management

Chiplets can add complex behaviors in terms of heat dissipation and thermal interactions between the chiplets and the substrates. Substrate stackup material and chiplet proximity have considerable impact on thermal and stress performance. For this reason, predictive analysis before or during the prototyping/planning phase is very important. Starting analysis as far left in the process as possible allows for maximum flexibility in making material choices and tradeoffs. Designers should generate power-aware thermal and stress device-level models to provide greater accuracy for thermal and mechanical simulations. Using a combination of chip-level and package/system thermal modeling, warpage, stress and fatigue points could be identified earlier in the design phase.

Test and Testability

Heterogeneous chiplet designs are very different from traditional designs. IEEE test standards are being developed to accommodate these 2.5D test methods. Different tool vendors may deploy different approaches in implementing these standards, which may cause test compatibility issues of chiplets that use different DFT vendor tools. For board level testing, a composite BSDL file for each of the internal components is preferred, but may not necessarily be supported by all DFT tool vendors, which further complicates the PCB level testing.

Although each chiplet is assumed to be delivered as a known-good-die (KGD), each still needs to be re-tested after being assembled into the 3D-IC package. As such, a production test program must be provided for each of the internal components of the 3D-IC package. The tests need to run from the external package pins, most of which are not connected directly to the chiplet pins. In addition to the individual die testing, the die-to-die interfaces between chiplets need to be functionally tested as well.

Driving Verification and Signoff

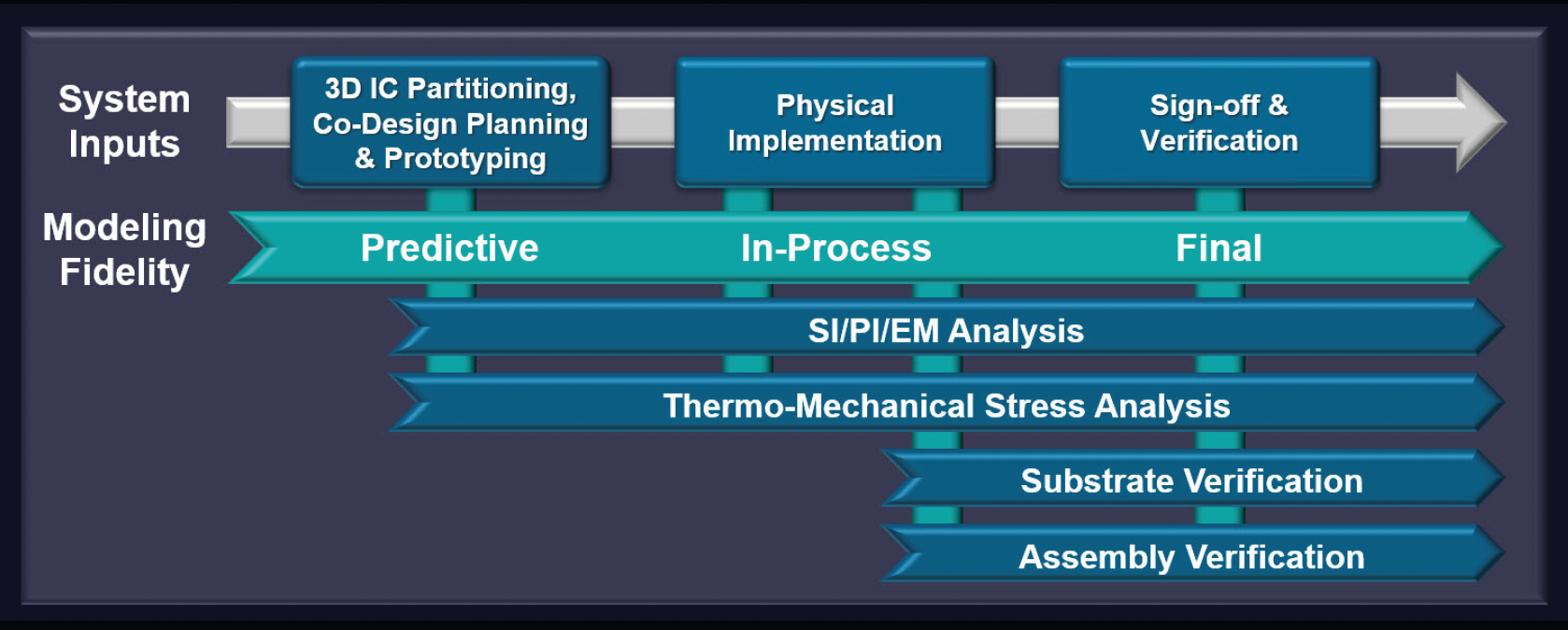

To be able to release into manufacturing with confidence, we have to make sure that all the devices and substrates work together as expected. For this, it is important to start verification in the planning process and continue throughout the layout process. Such in-design validation provides early identification and resolution of manufacturing issues without running the full sign-off flow. When it comes to final design verification, it is important to also analyze various layout enhancements that will improve yield and reliability.

For more details on the “Five Key Workflows that Deliver 3D IC Packaging Success”, you can download the whitepaper published by Siemens EDA.

Also Read:

A faster prototyping device-under-test connection

Share this post via:

Siemens U2U 3D IC Design and Verification Panel