Orr Danon is the CEO and Co-Founder of Hailo. Prior to founding Hailo, Orr spent over a decade working at a leading IDF Technological Unit. During this time he led some of the largest and most complex interdisciplinary projects in the Israeli intelligence community. For the projects he developed and managed, Danon received the … Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More

WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More

WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read More

Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read MoreHas ASML Reached the Great Wall of China

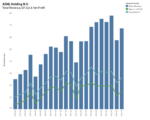

Is it time to abandon the ASML stock?

The first tool company to report Q2-24 results is ASML, and the lithography leader delivered a result above the guidance of EUR5.95B. Revenue of EUR6.242B is 4.9% above guidance and 18% above last quarter’s result of EUR5.29B.

Both operating profit and gross profit grew but not to the level of … Read More

Blue Cheetah Advancing Chiplet Interconnectivity #61DAC

At #61DAC, I love it when an exhibitor booth uses a descriptive tagline to explain what they do, like when the Blue Cheetah booth displayed Advancing Chiplet Interconnectivity. Immediately, I knew that they were an IP provider focusing on chiplets. I learned what sets them apart is how customizable their IP is to support specific… Read More

The China Syndrome- The Meltdown Starts- Trump Trounces Taiwan- Chips Clipped

- The chip industry got a double tap of both China & Taiwan concerns

- Bloomberg reported the potential for draconian China chip restrictions

- Trump threw Taiwan under the bus demanding “protection money”

- Over-inflated chip stocks had a “rapid unscheduled disassembly”

US looking to further restrict

… Read MoreEvolution of Prototyping in EDA

As AI and 5G technologies burgeon, the rise of interconnected devices is reshaping everyday life and driving innovation across industries. This rapid evolution accelerates the transformation of the chip industry, placing higher demands on SoC design. Moore’s Law indicates that while chip sizes shrink, the number of… Read More

How Sarcina Revolutionizes Advanced Packaging #61DAC

#61DAC was buzzing with discussion of chiplet-based, heterogeneous design. This new design approach opens new opportunities for applications such as AI, autonomous driving and even quantum computing. A critical enabler for all this to work is reliable, cost-effective advanced packaging, and that is the topic of this post.… Read More

Accelerating Analog Signoff with Parasitics

An under-appreciated but critical component in signing off the final stage of chip design for manufacture is timing closure – aligning accurate timing based on final physical implementation with the product specification. Between advanced manufacturing processes and growing design sizes, the most important factors determining… Read More

Scientific Analog XMODEL #61DAC

Transistor-level circuit designers have long used SPICE for circuit simulation, mostly because it is silicon accurate and helps them to predict the function, timing, power, waveforms, slopes and delays in a cell before fabrication. RTL designers use digital simulators that have a huge capacity but are lacking analog modeling.… Read More

PCIe design workflow debuts simulation-driven virtual compliance

PCIe design complexity continues rising as the standard for intrasystem communication evolves. An urgent need for more system bandwidth drives PCIe interconnects to multi-lane, multi-link, multi-level signaling. Classical PCIe design workflows leave designers with most of the responsibility for getting the requisite… Read More

The Immensity of Software Development the Challenges of Debugging (Part 1 of 4)

Part 1 of this 4-part series introduces the complexities of developing and bringing up the entire software stack on a System on Chip (SoC) or Multi-die system. It explores various approaches to deployment, highlighting their specific objectives and the unique challenges they address.

Introduction

As the saying goes, it’s… Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry