Douglas Smith has focused his career on optimizing advanced technologies for high volume ASIC applications. He has led elite design teams at Motorola SPS then Broadcom for over 25 years. With 200+ successful tape outs generating $10B+ in revenue. Douglas left Broadcom to self-fund a startup focused on advanced memory technologies.… Read More

From Point Solutions to Agentic AI Ecosystems: Semiconductor Process Control Depends on Its PastAgentic AI is often presented as a revolutionary…Read More

From Point Solutions to Agentic AI Ecosystems: Semiconductor Process Control Depends on Its PastAgentic AI is often presented as a revolutionary…Read More Panel Discission: Beyond Moore's Law and the Future of Semiconductor ManufacturingThe semiconductor industry is entering a post-Moore’s Law…Read More

Panel Discission: Beyond Moore's Law and the Future of Semiconductor ManufacturingThe semiconductor industry is entering a post-Moore’s Law…Read More CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More

CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read More

RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read More Bringing mathematical rigour in the world of hardware - a journey into Formal VerificationThis interview presents the first steps of Robert…Read More

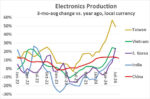

Bringing mathematical rigour in the world of hardware - a journey into Formal VerificationThis interview presents the first steps of Robert…Read MoreAsia Driving Electronics Growth

Electronics production in the major developed countries has been showing slow growth or declines in 2024. United States electronics production three-month-average change versus a year ago (3/12 change) was 0.4% in July 2024, the slowest since the pandemic year of 2020. Growth has been slowing since averaging 6.5% in 2022 and… Read More

Automating Reset Domain Crossing (RDC) Verification with Advanced Data Analytics

The complexity of System-on-Chip (SoC) designs continues to rise at an accelerated rate, with design complexity doubling approximately every two years. This increasing complexity makes verification a more difficult and time-consuming task for design engineers. Among the key verification challenges is managing reset domain… Read More

TSMC 16th OIP Ecosystem Forum First Thoughts

Even though this is the 16th OIP event please remember that TSMC has been working closely with EDA and IP companies for 20+ years with reference flows and other design enablement and silicon verification activities. The father of OIP officially is Dr. Morris Chang who named it the Grand Alliance. However, Dr. Cliff Hou is the one … Read More

The Immensity of Software Development and the Challenges of Debugging Series (Part 2 of 4)

Part 2 of this 4-part series reviews the role of virtual prototypes as stand-alone tools and their use in hybrid emulation for early software validation, a practice known as the “shift-left” methodology. It assesses the differences among these approaches, focusing on their pros and cons.

Safety Grading in DNNs. Innovation in Verification

How do you measure safety for a DNN? There is no obvious way to screen for a subset of safety-critical nodes in the systolic array at the heart of DNNs. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and now Silvaco CTO) and I continue our series on research ideas.… Read More

Collaboration Required to Maximize ASIC Chiplet Value

It is a well-known fact that chiplets provide several advantages over traditional monolithic chips. Despite these benefits, the transition to a chiplet-based design paradigm presents challenges that need coordinated efforts across the industry. In essence, collaborative efforts among various players involved are not … Read More

Andes Technology is Expanding RISC-V’s Horizons in High-Performance Computing Applications

By: Dr. Charlie Su, President and CTO, Andes Technology Corp.

At Andes Technology, we are excited to share some of our latest advancements and insights into the growing role of RISC-V in several high-performance applications. According to the SHD Group report, “IP Market RISC-V Market Report: Application Forecasts in… Read More

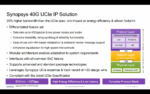

Synopsys Powers World’s Fastest UCIe-Based Multi-Die Designs with New IP Operating at 40 Gbps

As the demand for higher performance computing solutions grows, so does the need for faster, more efficient data communication between components in complex multi-die system-on-chip (SoC) designs. In response to these needs, Synopsys has introduced the world’s fastest UCIe-based IP solution, capable of operating at a groundbreaking… Read More

PQShield Builds the First-Ever Post-Quantum Cryptography Chip

Quantum computing promises to deliver vast increases in processing power. The technology exploits the properties of quantum mechanics to create revolutionary increases in performance. Medical and material science research are examples of fields that will see dramatic improvement when production-worthy quantum computers… Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!