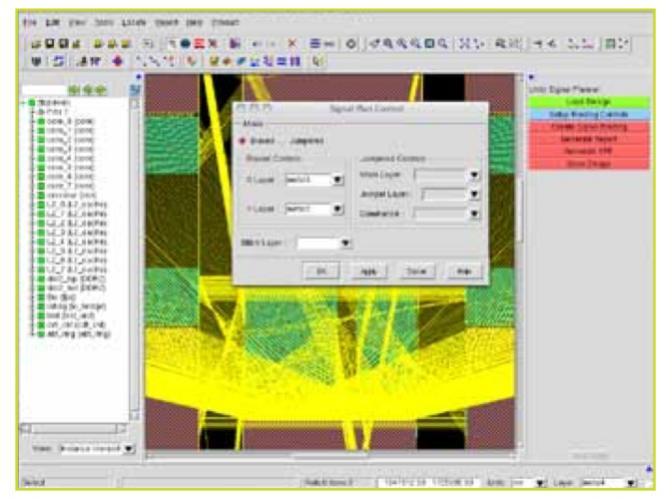

It is no secret that custom ICs are getting larger and more complex and this has driven chip design teams to split up into smaller teams to handle the manual or semi-automated routing of the many blocks and hierarchical layers that go to make up such a design. These sub-teams don’t just need to handle the routing within their own block(s)… Read More

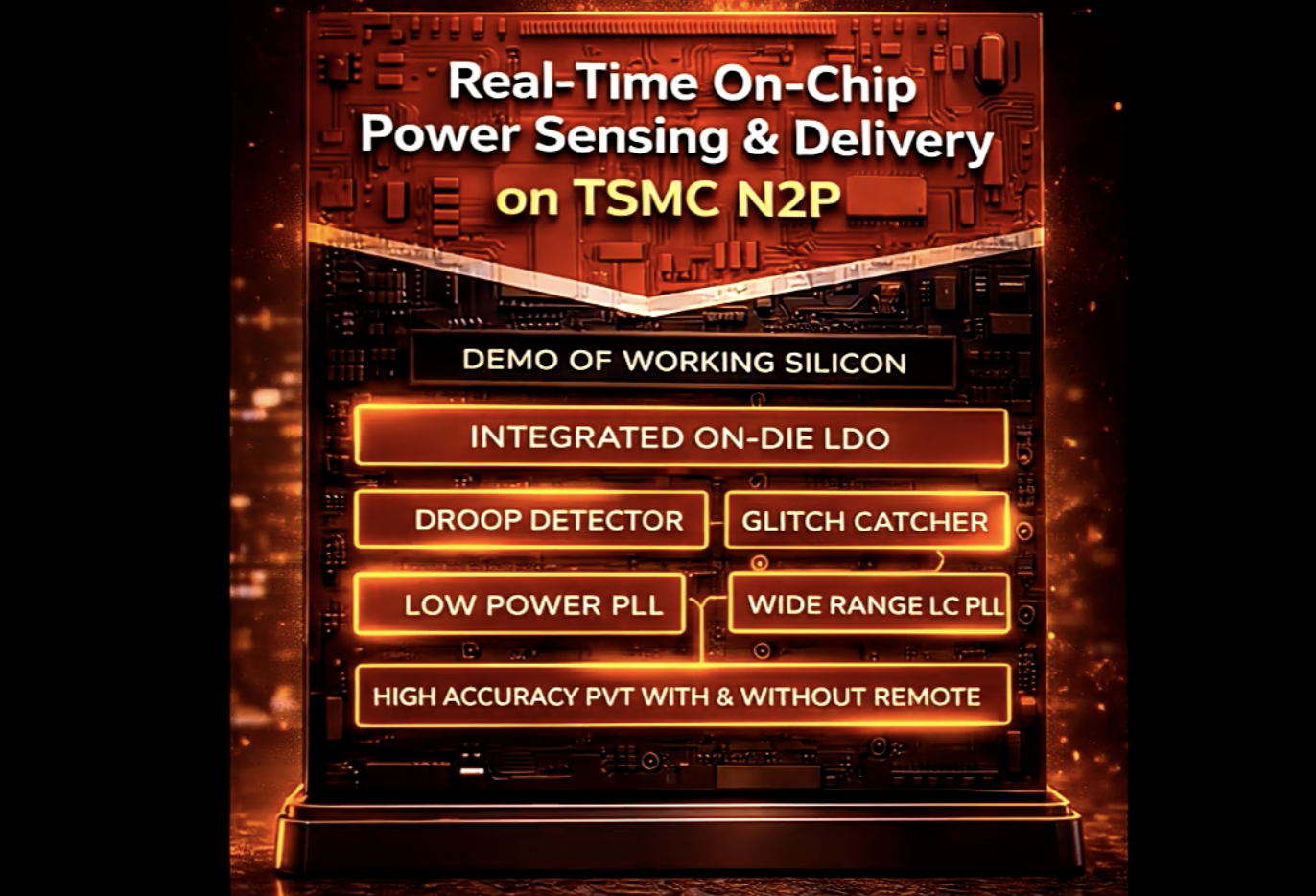

Analog Bits Demos Real-Time On-Chip Power Sensing and Delivery on N2P at the TSMC 2026 Technology SymposiumAnalog Bits has a way of stealing the…Read More

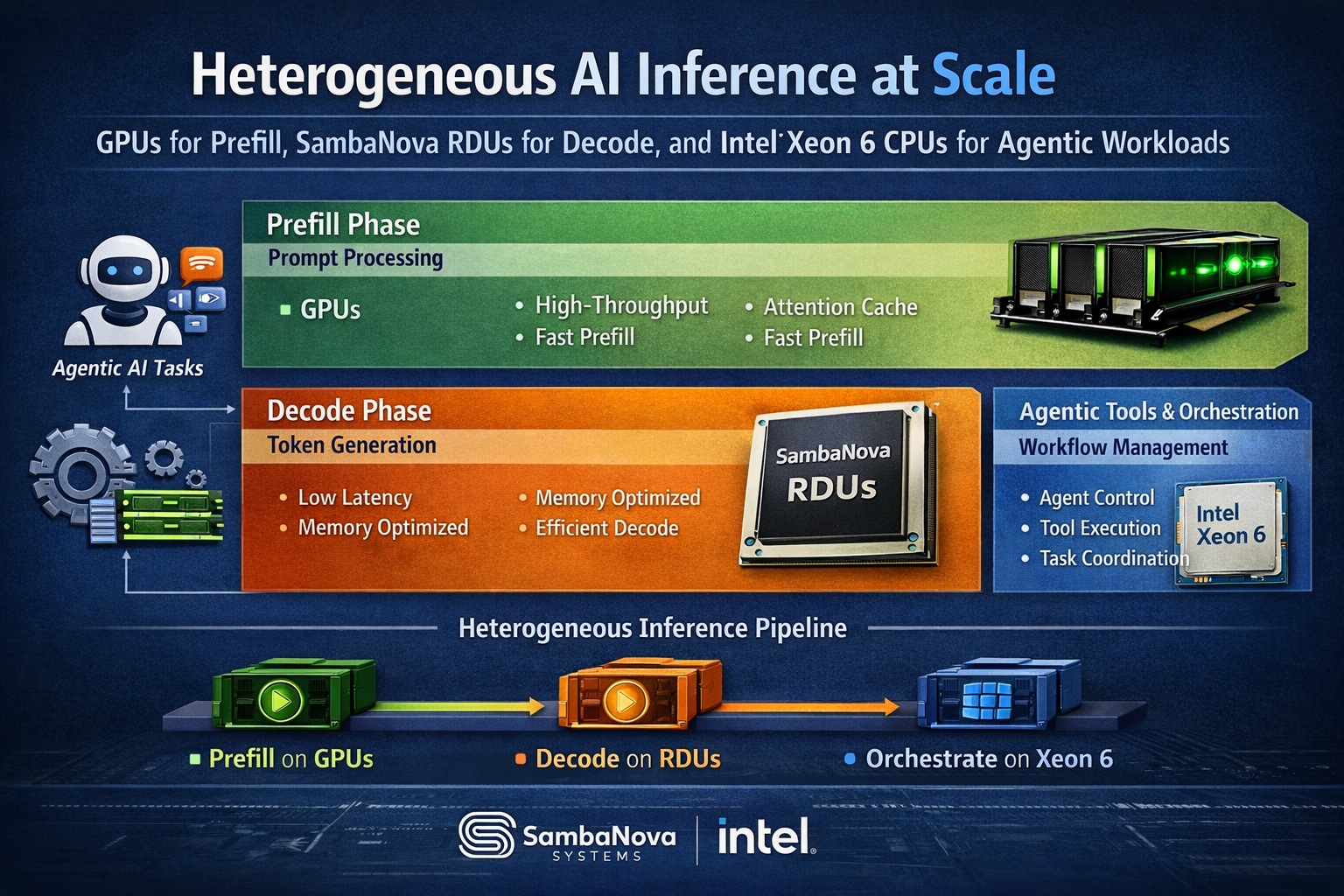

Analog Bits Demos Real-Time On-Chip Power Sensing and Delivery on N2P at the TSMC 2026 Technology SymposiumAnalog Bits has a way of stealing the…Read More Disaggregating LLM Inference: Inside the SambaNova Intel Heterogeneous Compute BlueprintSambaNova Systems and Intel have introduced a blueprint…Read More

Disaggregating LLM Inference: Inside the SambaNova Intel Heterogeneous Compute BlueprintSambaNova Systems and Intel have introduced a blueprint…Read More CEO Interview with Johan Wadenholt Vrethem of VoxoWith over two decades of experience bridging technology…Read More

CEO Interview with Johan Wadenholt Vrethem of VoxoWith over two decades of experience bridging technology…Read More TSMC to Elon Musk: There are no Shortcuts in Building Fabs!The opening of the TSMC 2026 earning call…Read More

TSMC to Elon Musk: There are no Shortcuts in Building Fabs!The opening of the TSMC 2026 earning call…Read More Speculation: Silicon’s Most Expensive CompulsionHow Time-Based Scheduling Reclaims Silicon Wasted by Speculative…Read More

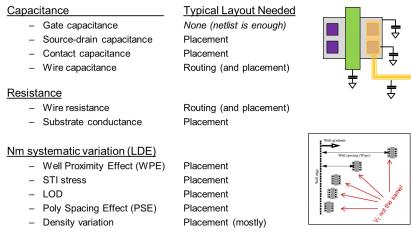

Speculation: Silicon’s Most Expensive CompulsionHow Time-Based Scheduling Reclaims Silicon Wasted by Speculative…Read MoreAnalog Constraint Standards

Over the years there has been a lot of standard creation in the IC design world to allow interoperability of tools from different vendors. One area of recent interest is interoperable constraints for custom IC design. Increasingly, analog design layout is becoming more automated. Advanced process nodes require trial layouts… Read More

Coby Hanoch joins Jasper

Jasper has hired Coby Hanoch as the VP of international sales to manage sales outside of North America. I talked to him last week.

Coby started his career after graduation from the Israeli Institute of Technology as an engineer at National Semiconductor. He quickly ended up in verification where they developed the first random … Read More

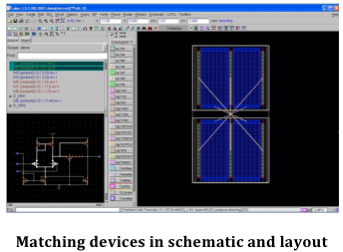

Nanometer Circuit Verification: The Catch-22 of Layout!

As analog and mixed-signal designers move to very advanced geometries, they must grapple with more and more complex considerations of the silicon. Not only do nanometer CMOS devices have limitations in terms of analog-relevant characteristics such gain and noise performance, but they also introduce new sources of variation… Read More

AMS Design, Optimization and Porting

AMS design flows can follow a traditional path or consider trying something new. The traditional path goes along the following steps:

[LIST=1]

PVT and Statistical Design in Nanometer Process Geometries

On Sept 22, 2011, the nm Circuit Verification Forumwill be held in Silicon Valley, hosted by Berkeley Design Automation. At this forum, Trent McConaghy of Solido DA will present a case study on the TSMC Reference Flow 2.0 VCO circuit, to showcase Fast PVT in the steps of extracting PVT corners, verifying PVT, and doing post-layout… Read More

Fast Track Seminars

Atrenta’s SoC realization seminars, “Fast Track Your SoC Design” have started.The first one was in Ottowa last Tuesday, and it was a full house. In a straw poll, most of the attendees acknowledged facing IP handoff and quality issues. The keynote speaker was Dr Yuejian Wu, director of ASIC development at Infinera… Read More

Phil Bishop and marketing at Magma

Earlier in the week I met with Phil Bishop, who is the corporate VP of worldwide marketing at Magma.

I started by asking him where he came from. He originally started as a designer at Motorola in microprocessors and microcontrollers. Then he moved to Silicon Compiler Systems (remember them?) who ended up being acquired by Mentor.… Read More

Tanner EDA Newsletter – Fall 2011

From the President: Another Great YearThanks to innovative, cost-effective technology and excellence in customer support, we’ve just ended fiscal year 2011 (on May 31st) with solid growth. Revenue was up 8%, we added 139 new customers, and we’re continuing to reach out to technology partners for MEMS and for the analog and mixed-signal… Read More

Simulating in the Cloud

Yesterday I met with David Hsu who is the marketing guy for Synopsys’s cloud computing solution that they announced at their user-group meeting earlier this year. It was fun to catch up; David used to work for me back in VLSI days although he was an engineer writing place and route software back then.

David admits that this is… Read More

Is Intel About to Take Flight?