If you have ever watched an experienced glass blower, your first thought is that they make it look so easy. I have had the opportunity to blow glass, and I can tell you that it is a constant struggle against temperature, time and muscles to get the glass to do anything like what you want. This is akin to what is required to take the elements… Read More

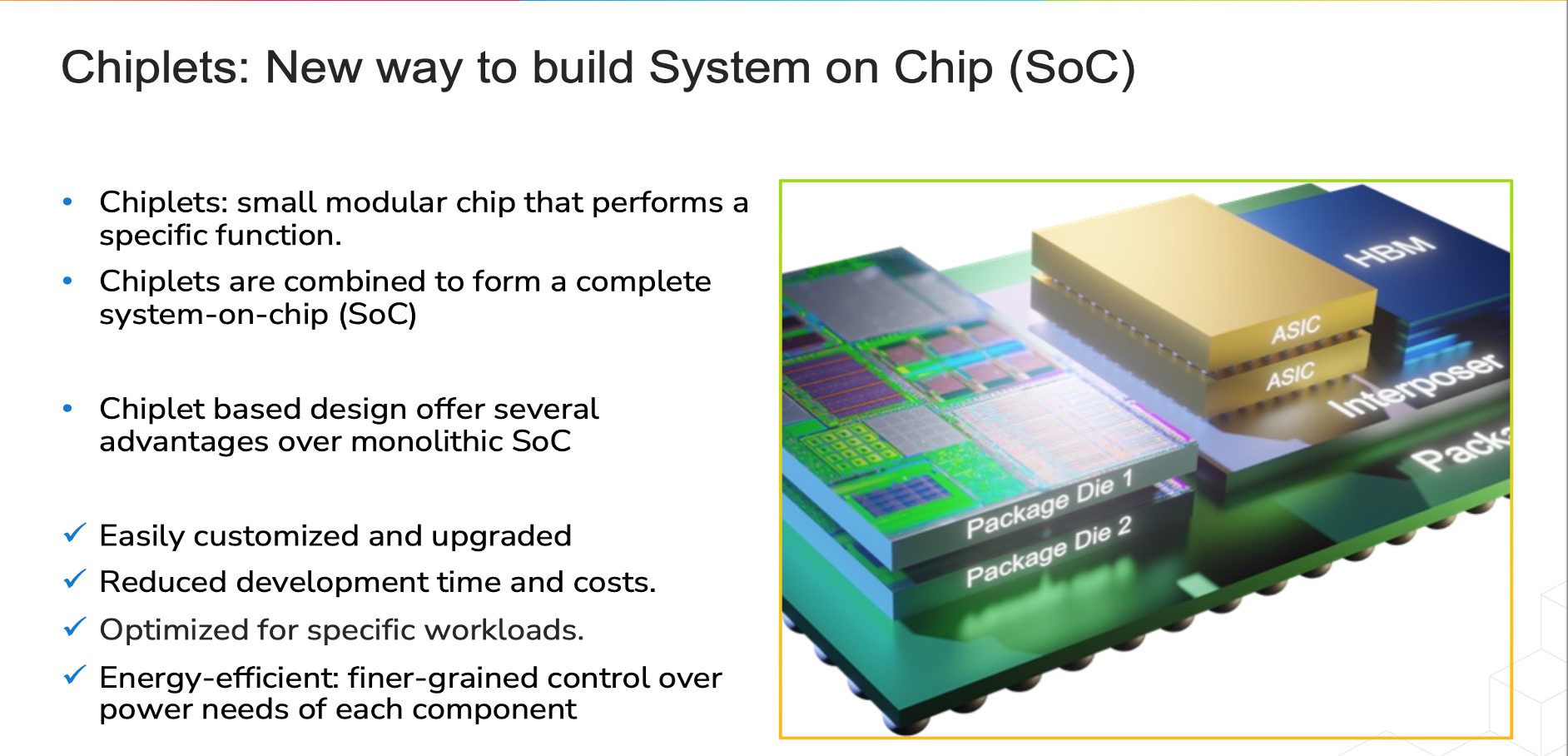

Streamlining Functional Verification for Multi-Die and Chiplet DesignsAs multi-die and chiplet-based system designs become more…Read More

Streamlining Functional Verification for Multi-Die and Chiplet DesignsAs multi-die and chiplet-based system designs become more…Read More S2C Advances RISC-V Ecosystem, Accelerating Innovation at 2025 Summit ChinaShanghai, July 19, 2025 — S2C, a leader in functional…Read More

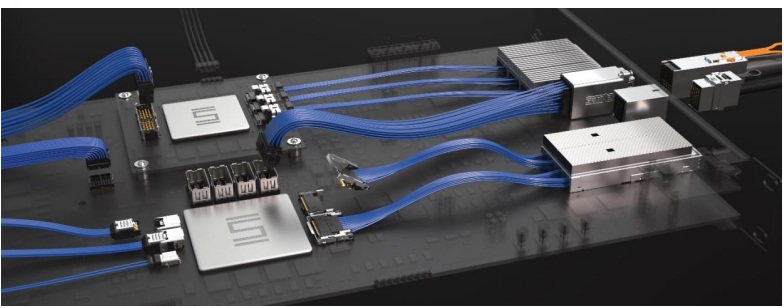

S2C Advances RISC-V Ecosystem, Accelerating Innovation at 2025 Summit ChinaShanghai, July 19, 2025 — S2C, a leader in functional…Read More Samtec Practical Cable Management for High-Data-Rate SystemsAccording to a recent Samtec whitepaper, in high-data-rate…Read More

Samtec Practical Cable Management for High-Data-Rate SystemsAccording to a recent Samtec whitepaper, in high-data-rate…Read MoreAccelerating Functional Safety Verification

Verifying a design for functional safety requirements for an IP or SoC per ISO 26262 is a complex process that can’t be encapsulated in one tool. Process complexities depend on whether the Tier1 or OEM is targeting safety-levels ASIL-A , B, C or D, where ASIL-D applies to anything truly safety-critical such as airbag controls or … Read More

WEBINAR REPLAY: ClioSoft Facilitates Design Reuse with Cadence® Virtuoso®

In September, ClioSoft gave a SemiWiki webinar titled, Reusing Your IPs & PDKs Successfully With Cadence® Virtuoso®. I was happy to be the moderator of this webinar, having had the chance to work with ClioSoft’s team over many years. The webinar was informative while also being very time efficient. I think it is important for… Read More

LRCX – A recovery without memory? Korea share gain? TSMC bonus?- all upside

LAM will likely bounce on Korea gains & TSMC

Memory still sucks but TSMC is hot!

Korea upside from share gains?

Japan/Korea – The “Beer Barometer”

Looks like a good Q3….

We think when Lam reports their Q3 this wednesday it will likely be a positive catalyst for the stock as we think the report will be better… Read More

Statistically speaking you probably care about On-chip Variation

There are some metaphorical similarities between reaching timing signoff and driving a car to your destination. Most of us get in the car, turn the key and push the gas pedal to make it go. While we might have a cursory understanding of what makes it go, there are actually a lot of “moving part” under the hood in each instance. For most… Read More

Safety and Platform-Based Design

I was at Arm TechCon as usual this year and one of the first panels I covered was close to the kickoff, hosted by Andrew Hopkins (Dir System Technology at Arm), Kurt Shuler (VP marketing at Arteris IP) and Jens Benndorf (Managing Dir and COO at Dream Chip Technologies). The topic was implementing ISO 26262-compliant AI SoCs with Arm… Read More

GLOBALFOUNDRIES and Arm Showcase Broad Range of Partnership

I previously blogged on the GLOBALFOUNDRIES (GF) Technology Conference (GTC) held in Santa Clara, CA. The main takeaway that I shared in that blog was that GF’s announced “pivot” to a specialty foundry announced over a year ago, including its decision not to pursue 7nm and smaller nodes, appears to be working and GF is gaining momentum.… Read More

WEBINAR: PAVE360 Validating Autonomous Vehicle Behavior

Siemens Mentor recently announced PAVE360™, a very cool comprehensive pre silicon simulation environment. Autonomous cars are very popular here in Silicon Valley and quite safe on the highways since the average speed is 25mph (horrible traffic). In the city you need autonomous parking unless you want to waste precious time … Read More

ASML – In Line Qtr but big bookings – Logic Strong! Memory ? EUV?

ASML in line QTR with big Orders

Near term slippage w long term upside

Logic is strong but memory recovery unknown

EUV is finally a reality/commercialized

In line quarter- supplier slippage expected in Q4

Results were revenues of Euro 3B and EPS of Euro 1.49, more or less in line with earnings estimate if a tad bit light in revenue. … Read More

TSMC – Solid Q3 Beat Guide- 5G Driver – Big Capex Bump – Flawless Execution

TSMC puts up solid QTR, Capex increase for 5NM and capacity increase, 5G/mobile remains driver- HPC good 7NM, 27% of revs- Very nice margins!

In line quarter-Good guide

TSMC reported revenues of $9.4B and EPS of $0.62 , more or less in line with expectations, perhaps a touch below ” whisper” expectations which had been… Read More

Should Intel be Split in Half?