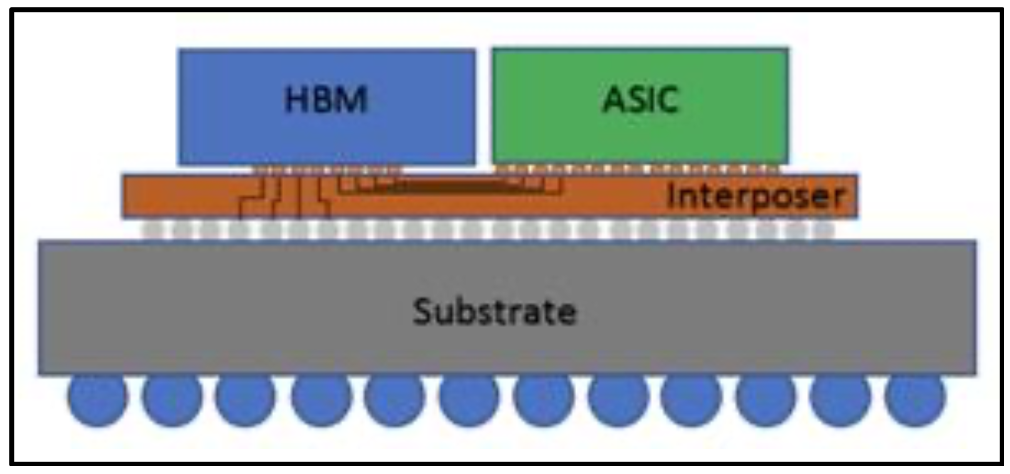

I have been watching the trend for quite some time now that many advanced FinFET designs today are actually 2.5D systems in package. All of these 2.5D silicon interposer-based designs have high-bandwidth memory (HBM) stacks on board. Often there are multiple memory stacks in both 4-high and 8-high configurations. If you follow what’s been called the “more than Moore” revolution associated with 2.5 and 3D design, you know that HBM memory stacks essentially paved the way for this revolution. The HBM memory specification is alive and well with new, high performance versions available today and more in the pipeline.

I have been watching the trend for quite some time now that many advanced FinFET designs today are actually 2.5D systems in package. All of these 2.5D silicon interposer-based designs have high-bandwidth memory (HBM) stacks on board. Often there are multiple memory stacks in both 4-high and 8-high configurations. If you follow what’s been called the “more than Moore” revolution associated with 2.5 and 3D design, you know that HBM memory stacks essentially paved the way for this revolution. The HBM memory specification is alive and well with new, high performance versions available today and more in the pipeline.

That’s why an upcoming webinar from SiFive caught my eye. Entitled SiFive HBM2/2E IP Subsystem: Features and Integration Guidelines, this webinar will take you through everything you need to know about the latest HBM standards and how to add HBM memory to your next chip. If you’re even considering the benefits of HBM memory stacks, you need to attend this webinar. The event will be hosted on Thursday, May 14, 2020 from 9AM-10AM and 6PM-7PM, Pacific Daylight Time. One of those time slots should work for you and you can register for the SiFive webinar here.

If you’re still on the fence about attending, here is some information that should help. The event will cover three aspects of HBM-based designs:

- Ketan Mehta, Director, SoC IP Product Marketing at SiFive will cover markets, applications and roadmaps

- Pranav Kale, Staff Engineer, SoC IP Engineering at SiFive will cover the features of the new HBM2/2E standards

- Ritam Das Adhikari, Manager, SoC IP Applications at SiFive will cover implementation guidelines for these technologies

I will have the honor of moderating the event. I’ve reviewed the presentation material with the SiFive team and I can tell you it’s quite complete. You should have an honorary degree in HBM design after attending. Let’s look at a few details to whet your appetite.

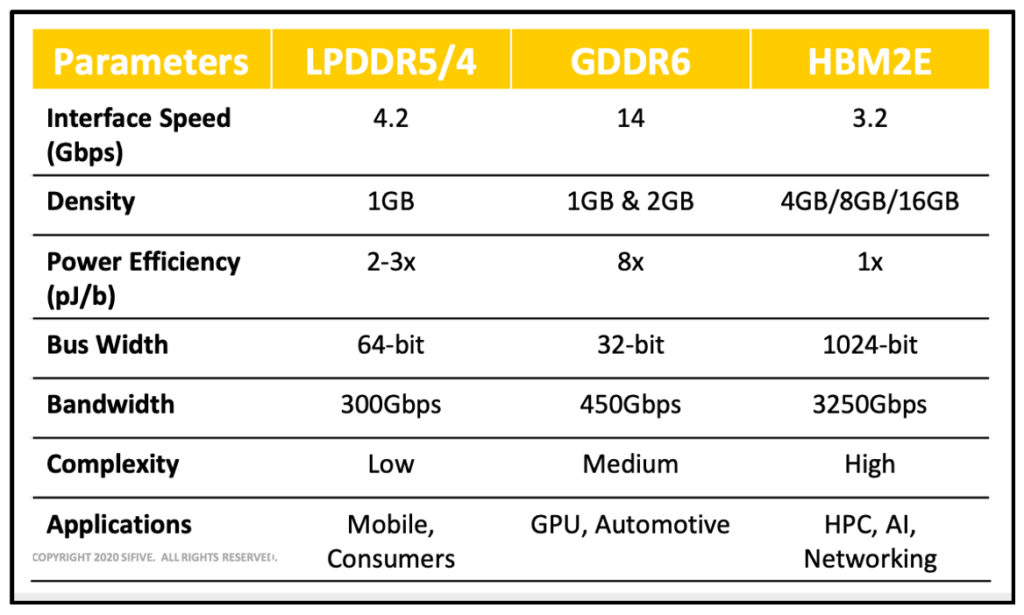

First of all, what is HBM and why do you need it? HBM memory stacks are actually very dense memory subsystems implemented with 3D packaging technology. The latest version of the specification is HBM2E. SiFive prepared a useful table below that summarizes what the latest HBM2E spec can deliver when compared with more traditional memory technologies. I would pay particular attention to the density, power efficiency and bandwidth rows.

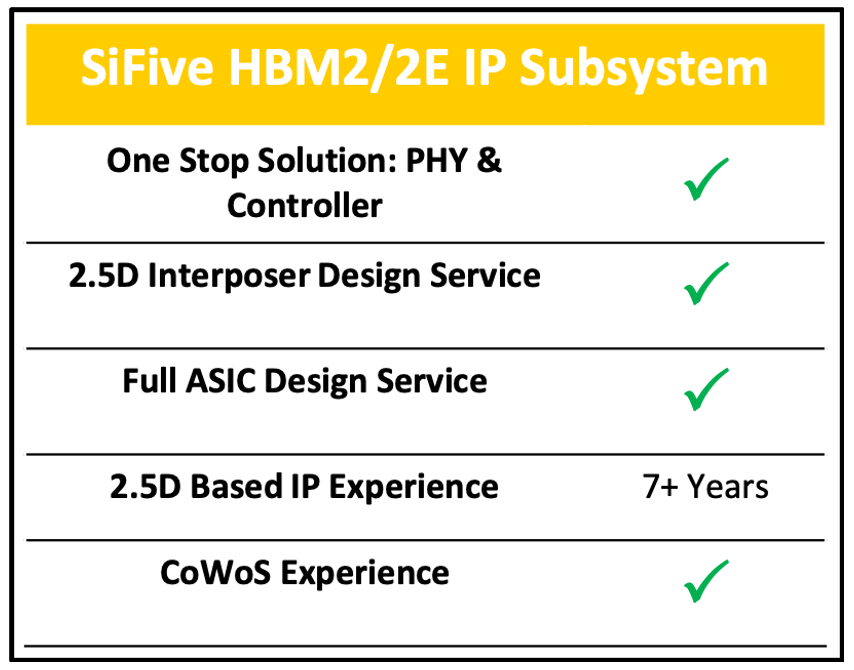

If your application needs ultra-dense, high-performance memory, HBM is really the only practical path forward. SiFive offers an HBM2/HBM2E IP subsystem that provides the critical elements of an Integrated HBM controller and HBM PHY that support both the HBM2 and HBM2E standards in multiple fab technologies. Below is a table summarizing the substantial technology and support offered by SiFive and their HBM2/2E subsystem. Note that CoWoS stands for chip-on-wafer-on-substrate, a 2.5D technology offered by TSMC.

The webinar goes on to cover popular applications for HBM technology, including high-performance computing, AI training/inference and networking. SiFive’s experience in these areas, as well as their technology roadmap are presented. You will also get a detailed overview of the extensive features and options supported by the SiFive HBM2/2E IP subsystem.

The webinar concludes with an overview of implementation guidelines for your next HBM design. The following items are all addressed:

- Key implementation guidelines

- HBM2/2E bump map

- HBM2/2E PHY orientation in ASIC

- Loopback support for testability

- DFT methodology debug tools

- Collateral available

- Support infrastructure

In short, everything you need to embark on an advanced 2.5D HBM-based design. There will also be a Q&A session with the presenters moderated by yours truly. As I’ve said, if you’re even thinking about HBM for your next design, you need to attend this webinar. You can register here. I hope to see you there.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.