We’re so spoiled by 4K and 8K and frame rates of 120 Hz or higher video content on high-performance devices that now, many of us expect these higher resolutions and rates on even small devices. The necessary interfaces exist in MIPI Display Serial Interface 2 (DSI-2) and Camera Serial Interface 2 (CSI-2). The challenge is these interfaces eat up a conventional SoC, either overwhelming low-end parts wholly or consuming too much power and battery life on a higher-end part. At MIPI DevCon 2022, Mahmoud Banna of Mixel co-presented with a customer, Hercules Microelectronics (HME), their solution: MIPI bridging DSI-2 and CSI-2 interfaces with an FPGA, providing acceleration at low power.

“Beyond mobile” applications for MIPI specifications

MIPI-powered displays have been ubiquitous in smartphones for some time. In most cases, smartphones feature high-end SoCs to power the complex cellular network interface and provide the multi-tasking response users expect. In exchange for access to high-performance content, users learned to take steps to save smartphone battery life, like dark mode, turning down the brightness, and more. It’s an acceptable trade most of the time.

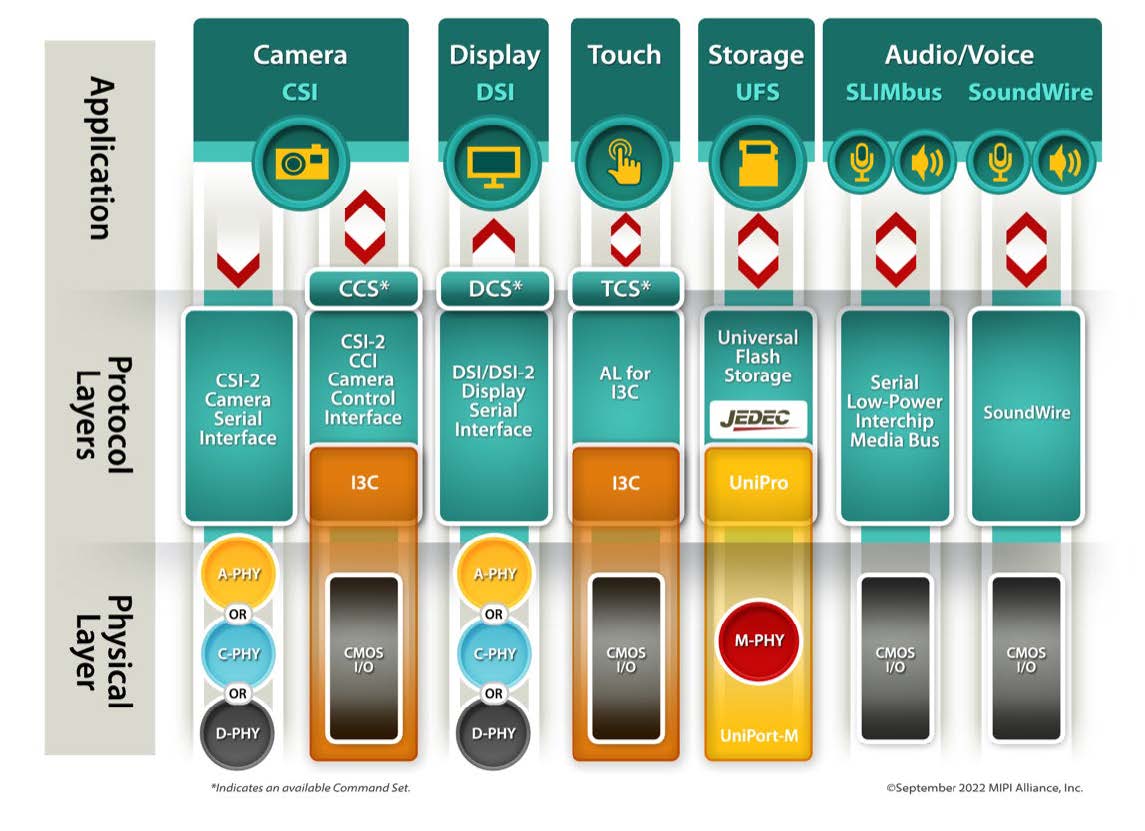

A new generation of “beyond mobile” applications demands the same type of performance without the same resources or management. High-performance displays and camera-based sensors now appear in automotive, IoT, wearables, industrial devices, and more. Bandwidth requirements are high, power requirements are low, and EMI is a concern anytime signals switch rapidly. MIPI developed its primary display and camera interface specifications from the ground up for these applications. The evolution of these specifications continues; DSI-2 v 2.0 was released in July 2021, and CSI-2 v 3.0 was released in September 2019.

Splitting the difference with FPGA-based MIPI bridging solutions

Most of these new applications operate in consumer segments with short lifecycles or industrial segments with relatively low volumes. Add to those factors the ongoing enhancements of the MIPI specifications, and designing an ASIC becomes risky. It’s easy to miss a market window, a critical new feature, or cost targets, and seeing a device with an outdated specification raises questions among buyers.

An FPGA could solve many of those concerns. FPGAs enable faster prototyping and proof of concept, enabling companies to demonstrate devices for investors. FPGAs allow customization, using the same basic elements in more than one design, or quickly targeting a new use case. Risks of a hardware re-spin shrink, with the ability to reprogram logic. And FPGA-based reference designs allow OEMs to do their tweaking to unique requirements.

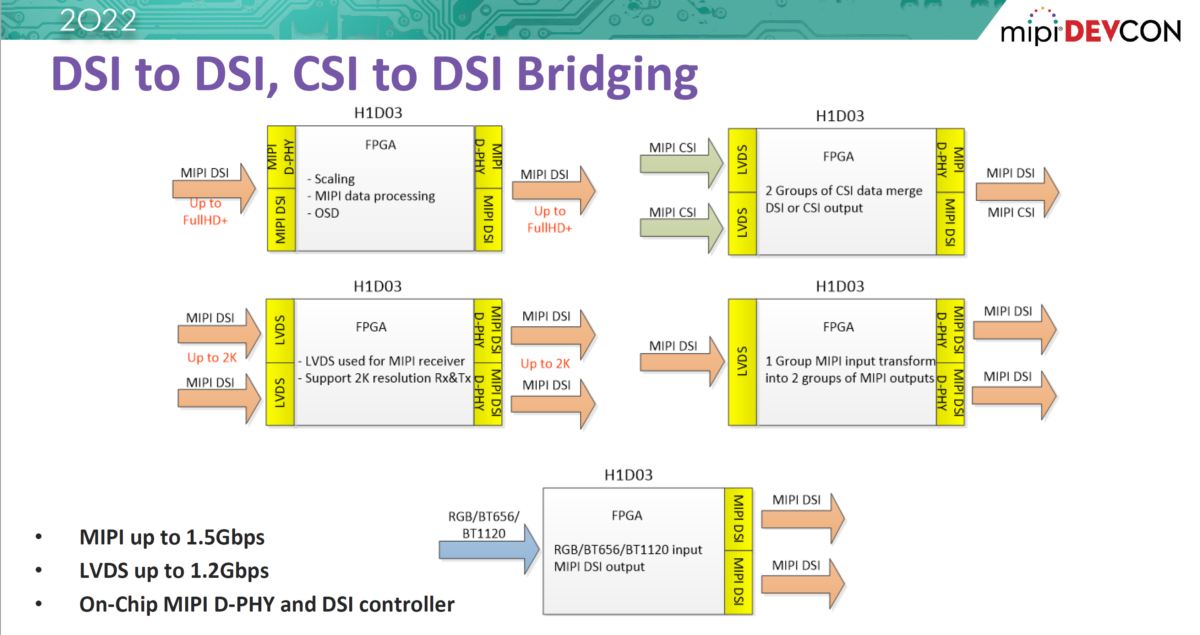

There’s still the challenge of power consumption. A mid-range FPGA on a newer process technology node can offer the right baseline of power use while still delivering the logic size and performance needed. “The traditional way to build a MIPI bridging system over an FPGA was to use the FPGA LVDS interface to emulate the MIPI interface,” says Banna. “But the growing trend here is to harden the MIPI subsystem, including the PHY and the controller, to achieve many benefits.” Hardened MIPI D-PHY and DSI-2 controller IP from Mixel hit higher data rates, are more stable in FPGA contexts, and consume less power.

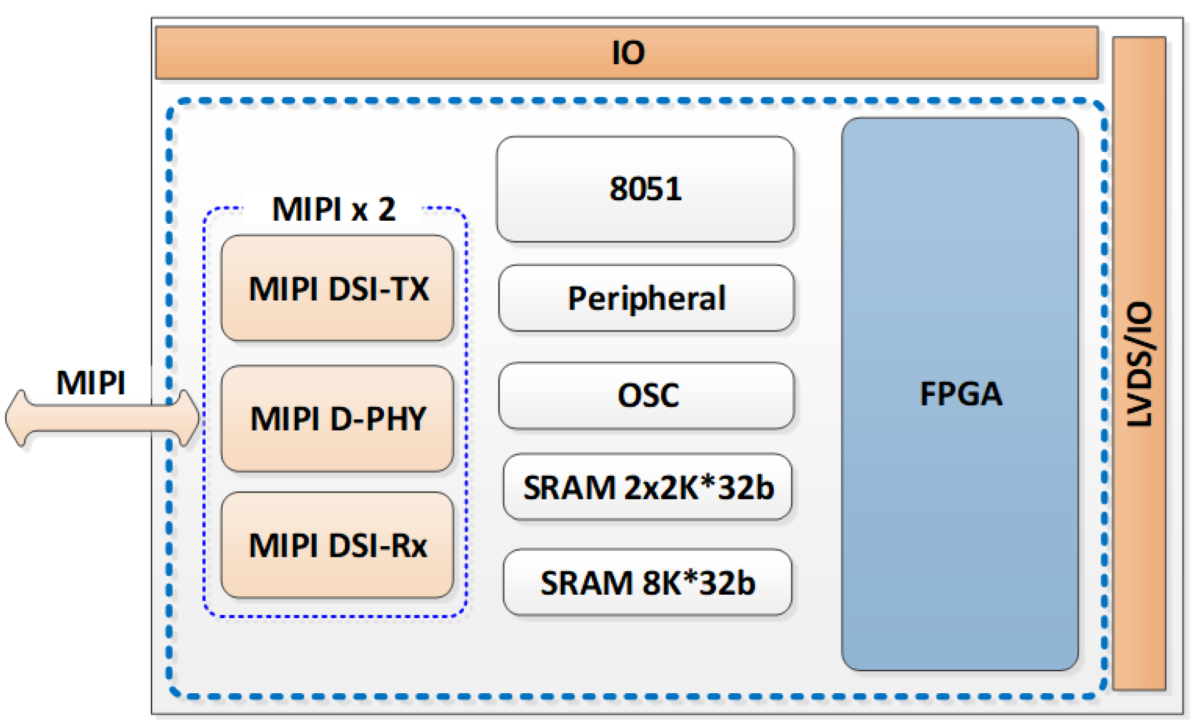

Illustrating the concept, Mixel is teaming with Hercules Microelectronics and their H1D03 FPGA. Built on a 40nm LP process, the H1D03 pairs two hardened Mixel MIPI IP blocks with an 8051 microcontroller, two SRAM blocks, 2K LUTs running at up to 200 MHz, and LVDS and other I/O.

Wide range of possibilities for MIPI bridging

Configuring the MIPI D-PHY, MIPI DSI-2, and LVDS blocks for emulating CSI-2, this approach can hit many use cases. Yundong Cui of HME offers this diagram:

In the recorded video of the MIPI DevCon 2022 session, Cui steps through several applications for the H1D03. His examples include a low-end cellphone or tablet, an AR headset, an e-Paper display, a smart home control panel, and an industrial camera. In each case, he points out how offloading the SoC improves system performance while keeping power low. Banna takes on some questions in a short Q&A and highlights upcoming MIPI PHY IP on the Mixel roadmap.

Hardening the Mixel MIPI IP is an important step here. These latest MIPI specifications are complex, and hardened IP ensures consistent performance regardless of what happens in the FPGA. It also removes the burden for the OEM to try to debug a soft implementation so they can focus on functionality in their application.

To see how Mixel and Hercules Microelectronics work together in MIPI bridging DSI-2 and CSI-2 interfaces with an FPGA, view the entire MIPI DevCon 2022 session on YouTube at:

Leveraging MIPI DSI-2 & MIPI CSI-2 Low-Power Display and Camera Subsystems

Also Read:

MIPI in the Car – Transport From Sensors to Compute

A MIPI CSI-2/MIPI D-PHY Solution for AI Edge Devices

FD-SOI Offers Refreshing Performance and Flexibility for Mobile Applications

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.