Semiconductor IP is the fastest growing market inside the fabless ecosystem, it always has been and always will be, especially now that non-traditional chip companies are quickly entering the mix. Towards the end of the year I always talk to the ecosystem to see what next year has in store for us and 2018 looks to be another year of double digit growth for IP companies, absolutely.

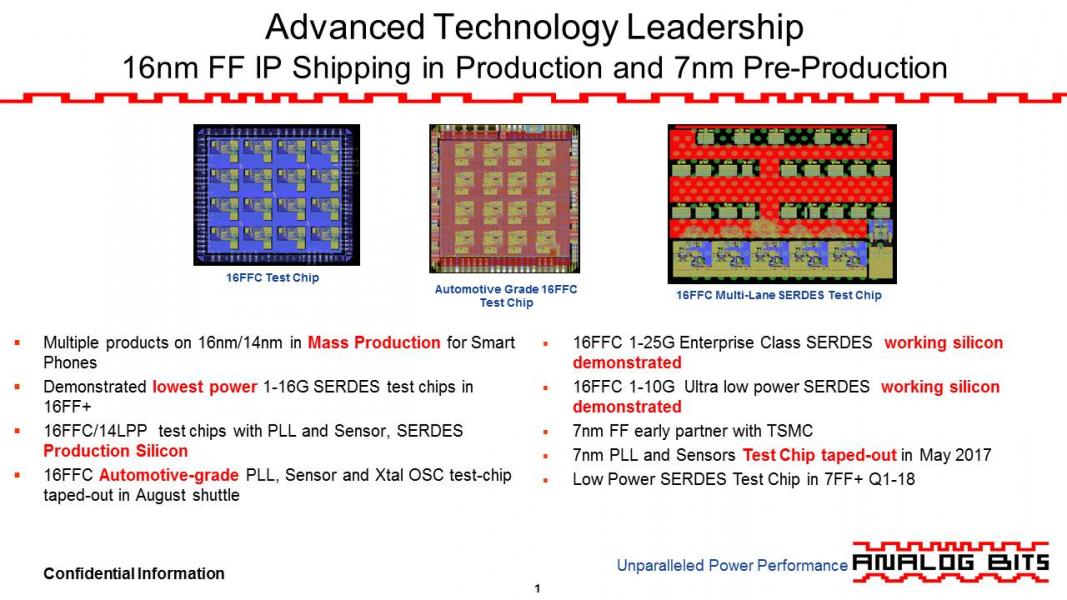

One of the more interesting conversations we have had (Tom Dillinger and myself) was with Analog Bits CEO Alan Rogers and EVP Mahesh Tirupattur. Analog Bits is well known for high performance and low power mixed-signal IP including SERDES which brings us to the most interesting part of our discussion and that is 7nm design and qualification challenges:

What are the major challenges for advanced node SERDES design?

“Starting with 28nm, we realized we had to re-think our design approach. We looked at our SERDES microarchitecture and layouts. We had to design the metal first, then the devices, then do our schematic based analysis. High-speed is a metal-dominated design.”

What are the analysis challenges in advanced nodes?

“EM, for sure. I*R voltage drop. RC delays will continue to be problematic.”

How do you support the greater diversity in back-end technology options?

“As an IP provider, the fewer metal stacks we have to support is better. The first 4-6 base levels are pretty standard. We do customer-driven customizations for the top metals, to embed inductors, distribute clocks, and meet the customer’s specific pad technology.”

At 7nm, there are additional constraints on physical design and analysis flows. Parameter variations are a major issue. How are you addressing those new requirements?

“We’re finding that reliability tools are a weak point. Rather than using pass/fail criteria, we need to understand design margins. For physical design, the series gate resistance of the FinFET is an increasing issue. We’re limiting the number of fins, and double-driving from both input ends. That has an impact on our layout styles, as well.”

How are you balancing technology scaling with increasing difficulty in meeting reliability targets, such as ESD?

“Our customers expect us to use the standard, qualified ESD structures from the foundry. We have to design our I/O circuits to meet the target matching impedance of the system at the frequency of interest, say 50 ohms. That implies adding inductance to offset the ESD capacitance. It impacts area, and introduces some channel loss, which impacts the overall cost.”

The application markets for 7nm are quite diverse, introducing requirements such as temperatures up to 150 degrees C. How has that been an impact?

“Leakages at 150 are higher… they all add up. Again, it comes down to cost.”

What modeling and/or CAD challenges are present at advanced nodes?

“IBIS-AMI modeling is becoming a must have that we need to provide to our customers.”

Any other SERDES design challenges that you would like to highlight?

“More customers are needing SERDES for data transmission requirements. We’re seeing SERDES I/O banks 2 or 3 deep, on all 4 sides of the die. Our IP must be designed to be arrayable in multiple dimensions. Even consumer applications, such as video transmission, are requiring greater transmission bandwidth — that adds to the cost of the silicon, to be sure, but increasingly, the package and PCB are becoming a greater cost factor.”

About Analog Bits

Founded in 1995, Analog Bits, Inc. (www.analogbits.com), is a leading supplier of mixed-signal IP with a reputation for easy and reliable integration into advanced SOCs. Products include precision clocking macros such as PLLs & DLLs, programmable interconnect solutions such as multi-protocol SERDES and programmable I/O’s as well as specialized memories such as high-speed SRAMs and TCAMs. With billions of IP cores fabricated in customer silicon and design kits supporting processes from 0.35-micron to 7-nm, Analog Bits has an outstanding heritage of “first-time-working” with foundries and IDMs.

Comments

One Reply to “7nm SERDES Design and Qualification Challenges!”

You must register or log in to view/post comments.