PCI-SIG has held to doubling PCIe’s data rate with each revision of the specification. The consortium of 800 companies, with its board consisting of Agilent, AMD, Dell, HP, Intel, Synopsys, NVIDIA, and Qualcomm, is continuing this trend with the PCIe 6.0 specification which calls for a transfer rate of 64 GT/s. PCI-SIG released the final specification for PCIe 5.0 in May 2019. This revision is gaining traction in the marketplace, however the needs of many market segments, such as HPC, are already creating strong interest in PCIe 6.0. PCIe 6.0 is expected to be finalized this year, but with completion of draft 0.7 it is already stable enough for development of IP and test silicon.

In PCIe 6.0 many changes are being made to meet the higher data rate requirement. Synopsys offers a very informative technical bulletin titled “Successful PCI Express 6.0 Designs at 64GT/s with IP” written by Gary Ruggles, Senior Product Marketing Manager, that articulates what these changes are. To double the data rate from 32 GT/S to 64GT/s it is necessary to move from NRZ to PAM-4 signaling. This in turn necessitates a new error correction strategy. Variable size Transaction Layer Packets (TLPs) used previously are being packed into fixed size Flow Controller Units (FLITs). In addition to this, there is a new low power state, L0p, which will help with rapid power/bandwidth scaling.

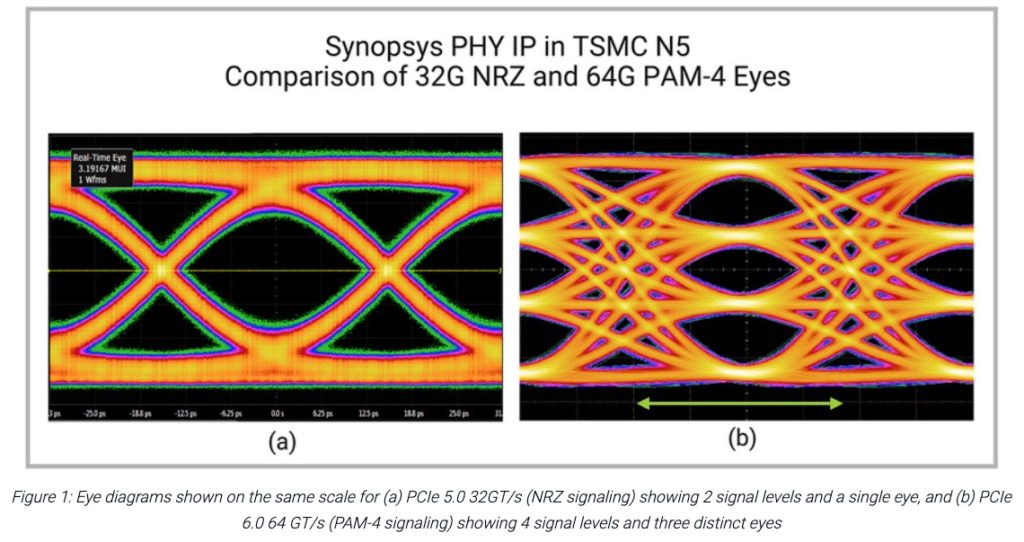

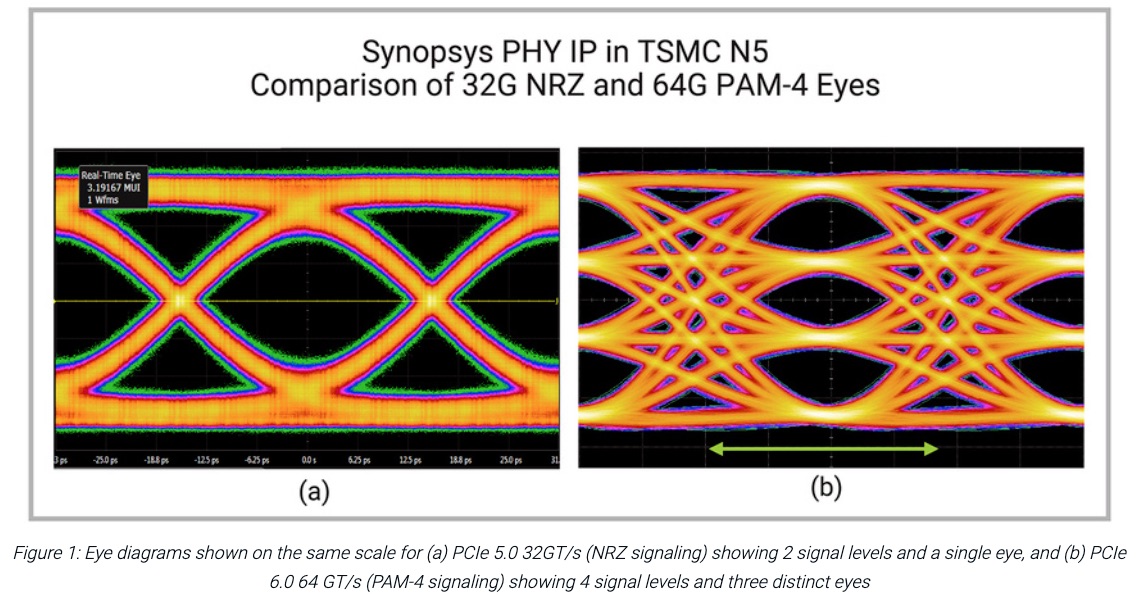

The biggest change is adoption of PAM-4. If PCIe 6.0 continued to use NRZ, the increased data rate would have had to come from a doubling to the frequency, which would have been accompanied with a deterioration in channel losses. The Nyquist frequency would have doubled to 32 GHZ, causing channel losses of 60db, which is too high for a workable system. PAM-4 offers a doubling of the data transmitted by utilizing 4 signal levels instead of 2. The tradeoff is that the eye regions in each transition are smaller, so the signal is more vulnerable to noise.

Improved RX design is required, which leads to using an ADC and digital signal processing to ensure improved receive performance. This also makes it easier to provide legacy support for previous versions using NRZ. Even with improved RX design there will be issues in the channel, including the package and board, that will cause higher error rates. The PCIe 6.0 specification includes the use of forward error correction (FEC) to mitigate the higher bit error rate (BER). To avoid higher latency the PCI-SIG calls for a lightweight forward error correction (FEC) coupled with the use of cyclic redundancy codes (CRC) to detect bad packets.

PAM-4 encoding and the addition of FEC required the change to FLITs with fixed size packets of 256 bytes. Multiple TLPs may be combined into a single FLIT or may span several, depending on their size. In PCIe 6.0 TLP and DLP headers have changed and no longer include their own CRC because the CRC checking occurs at the FLIT level now. Also, PHY layer framing tokens are no longer needed.

The Synopsys technical bulletin also covers the new low power state mode and how it operates to avoid delays during mode change. There is a section of how increasing the number of available tags helps boost performance. In closing there is a discussion on the testing and debug challenges that come with PCIe 6.0 based designs. PAM-4 is more complex than NRZ, making it important that there is support for built-in loopback modes, and pattern generators & receivers in the PHY and controller IP. Also, to improve the development process PCIe 6.0 IP should have support for debug, error injection and monitoring capabilities.

Even though there is still some time before the final PCIe 6.0 specification is approved, we can expect to see that companies which build PCIe based products will want to hit the ground running. Synopsys is offering PCIe 6.0 IP right now to help those companies prepare for this upcoming version. The technical briefing is a good source of information about PCIe 6.0 and what is changing. It is available on the Synopsys website along with the announcement of their complete IP solution for PCIe 6.0.

Also Read:

How PCI Express 6.0 Can Enhance Bandwidth-Hungry High-Performance Computing SoCs

Why In-Memory Computing Will Disrupt Your AI SoC Development

Using IP Interfaces to Reduce HPC Latency and Accelerate the Cloud

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.