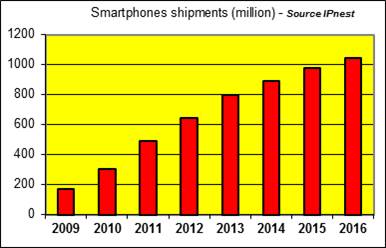

Network on Chip (NoC) technology is probably one of the most fascinating new concepts that has been developed and is implemented in real chips. NoC can be integrated into various System on Chip (SOC), targeting several market segment: Video Processing, Consumer Electronics, Automotive, Networking, Multimedia (digital TV), but the vast majority of Application Processor SoC, targeting mobile segment (smartphone or media tablets) do include a NoC. Let’s have a look at the SC market dynamic in 2012, as it was forecasted by Gartner in December 2011:

Application Processor is clearly the segment exhibiting the higher growth area (+117%). This means that the design teams in charge of such designs, working with Qualcomm, TI, Nvidia, Samsung, Mediatek or Rockchip (to just name few), will get the highest Time To Market (TTM) pressure you can imagine, but not only, as they are required to provide the best possible optimization in term of power, performance and area. That is, before releasing their design to prototyping (or even layout), they will have done many architectural passes. Here come the NoC.

Some of these teams prefer to use internally developed solution, but we can see now that a majority tend to use an existing solution available as an Intellectual Property (IP) function. We clearly see that the chosen solution is FlexNoC from Arteris, as we have shown in this post. Semiconductor customers such as Samsung, Qualcomm and TI have standardized on the Arteris NoC for their application processors and more complex modem basebands.

The NoC integration allows to interconnect (multiple) CPU, GPU, DSP, on chip memories, off chip DRAM through the DDRn memory controller, and the various functions from video accelerator to audio processor and from SuperSpeed USB to MIPI DSI or HDMI. If NoC functionality would only be to interconnect all these pieces, it would already be useful, when you consider that, in 2012, an Application Processor SoC integrates about one hundred IP, like for example with OMAP5 from TI! The NoC real power is to create an autonomous communication Network within the chip, has we have explained here.

Implementing NoC technology as a customer-ready product requires years of close customer interaction and integration work with tools in the EDA design flow. Arteris is way ahead in this, since they have been working with customers on super sophisticated chips since 2006 and have really demanding customers like Qualcomm, TI and Samsung. Creating a complete NoC product requires not only fully verified RTL output, but advanced internal simulation for quick what-if analysis, “Virtual Prototyping” for system-level design and performance verification, and links with all the EDA tools, especially an automated verification testbench environment like Arteris FlexVerifier.

Moreover, the Because of this high level of integrations, the Arteris NoC will allows a faster SoC integration and I should rather say a better optimized SoC, integrated faster. Indeed, when SoC architect is working to optimize the IC architecture, he has the possibility to do “Virtual Prototyping”, using for example Carbon Design Systems, the integrated FlexExplorer simulation set of tools to optimize a fabric (another name for the NoC), and literally play with the SoC architecture, change it, improve it, as he can explore the various possibilities. He can also export SystemC models for use within Synopsys Platform Architect are Carbon SoCDesigner to create a system-level far much faster with virtual prototype concept thanmore quickly and that runs faster than by doing traditional RTL simulations. Don’t forget: power, performance and area are the three magic words the design architect has to keep in mind during chip integration. Virtual prototyping the SoC has allowed him to optimize performance. In fact, you can select the fastest CPU core on the market, but if you don’t manage properly the data flows, you will end up with a fraction only of the expected performance.

For example, why should you running run your NoC at frequency range above GHz, when the limiting factor will be the memory controller, running at half a GHz maximum? If you do it, run your NoC at GHz range when the memory controller runs at 500 MHz or so, you just waste power! Of course it is possible to create a 1GHZ+ NoC because the technology is based on synthesizable RTL and is only limited by the chosen semiconductor fabrication process. It just isn’t smart to do it.

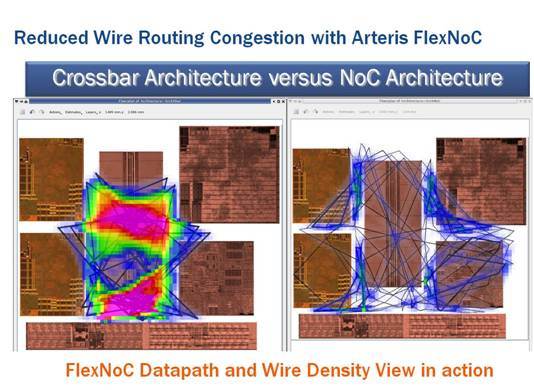

What’s about area? We have to remember that these Application Processors are sold by dozens of million units, so you can imagine the cost of the single square mm you can save! Very often, a picture value more than words: on the above picture, you can see, on the same SoC design that the routing congestion (left) linked to a crossbar architecture used for interconnects has disappeared when you have moved to a NoC based architecture. Everybody who has once been involved in real chip design knows the cost of layout iterations in term of TTM. You can save (lose) months if you have to reiterate the full process again and again.

So, you are now convinced that NoC (or chip fabric) are one of the best technologies which emerged during these last 5 to 10 years?

Then, you have joined Sonics, a company who has sold crossbar switches based chip fabric during the last ten years, and has suddenly discovered that the NoC based architecture was far better, as they have communicated recently in DeepChip. I think this communication from Sonics is the best tribute you could make to NoC architecture, as it comes from a company claiming that 1 billion IC have been shipped in production by Sonics customers… all of them using crossbar switches! Arteris claims that (only) 100 million IC have been shipped, designed by Arteris’ customers, but all of them without exception are using FlexNoC Network on Chip.

Bravo Sonics, better too late than never!

Eric Esteve

Share this post via:

Comments

0 Replies to “After 10 years promoting crossbar switch for interconnects, Sonics finally admit that NoC is better”

You must register or log in to view/post comments.