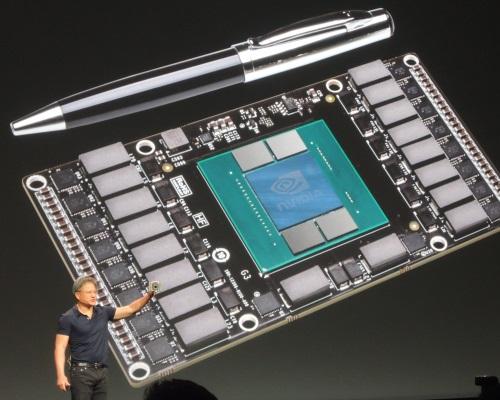

The use of silicon interposers is growing. Several years ago Xilinx broke new ground by employing interposers in their Virtex®-7 H580T FPGA. Last August Samsung announced what they say is the first DDR4 module to use 3D TSV’s for enterprise servers. Their 64GB double data rate-4 modules will be used for high end computing where capacity and performance are critical. Nvidia has announced that it is following its Maxwell GPU’s with the Pascal family that will use 3D memory and an interposer. This with other improvements promises a huge improvement in performance. The 3D interconnect will allow a 3X improvement in memory bandwidth, making Pascal 10X faster overall than Maxwell.

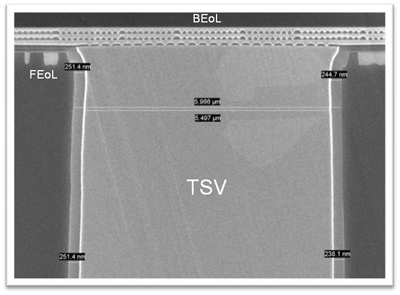

But interposers present challenges to design engineers. Unlike package substrates or wire bond connections, silicon interposers are made of silicon, a poor dielectric. Depending on the design configuration there are needs to pass signals vertically, which requires going through the silicon interposer or die themselves. The only way to achieve this high interconnect density is to use through silicon vias (TSV’s). These are metal vias that are relatively large and tall. They require insulation which is provided in the form of a silicon oxide sleeve separating the TSV metal from the silicon bulk.

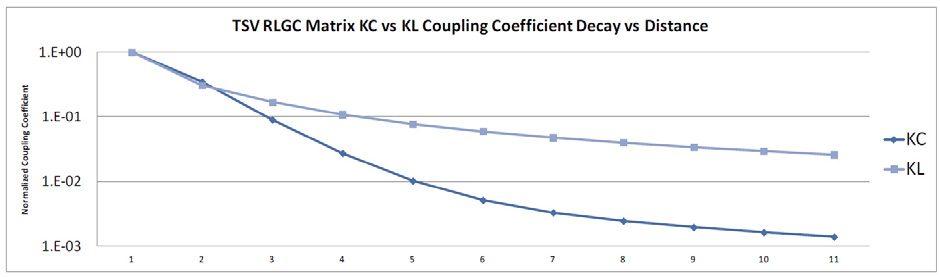

Their design structure and characteristics in high speed designs mandate analysis and modeling that will be accurate enough to predict potential performance issues. In advanced designs there will be high densities of TSV’s, which means there will be interactions between adjacent TSV’s. Simple RC extraction will not be sufficient. Nearby TSV’s can couple inductively. Also because of the properties of the interposer there will be parasitic MOS capacitors formed that can couple between adjacent TVS’s. The models needed to accurately represent this system should have frequency dependent elements.

I came across an excellent discussion of modeling and analysis of designs with multiple TSV’s recently that was published by Mentor.Here is the link. This paper discusses the difficulties in producing good compact models for TSV’s. It further discusses the tradeoff between full wave and quasi-static analysis methods in light of the many frequency dependent effects that need to be considered.

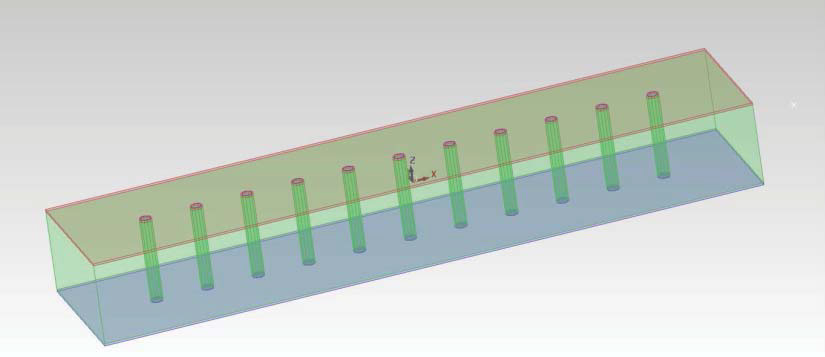

Mentor acquired Nimbic a while back and the test cases in the white paper that illustrate the results were run with nApex, which came from this acquisition. nApex is a quasi-static extractor, but is able to do some clever things to get good correlation with full wave solvers, which run much slower and also have the added difficulty of outputting S-parameters. Getting from S-parameters to compact models suitable for transient SPICE can be extremely difficult. When the target application is modeling large numbers of TSV’s there will be a high port count that almost always makes simulation difficult without an equivalent circuit.

The Mentor paper shows results for a test case modeled from DC up to over 100GHz. It drills into the relative effects of inductive and capacitive coupling within a TSV array as a function of distance. In real world cases there will also be RDL and potentially package structures that need to be included. All of this makes an effective case for using quasi static methods that can be shown to do well in modeling skin effects, etc.

The need to model 3D structures is only going to grow. It will be interesting to see how overall system performance improves as these new design approaches offer ways to reduce memory access time and expand inter-die busses. Nvidias successor to Pascal has already been discussed and the projected performance gains allow them to track Moore’s Law type improvements in their GPU’s. This certainly would not have been possible without the benefits of 3D memory and interposers that rely on TSV’s.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.