Semicon Enthusiast

New member

Hello folks,

I am currently diving deeper into the front-end of semiconductor processing and checking multiple sources to learn how it works. I came across multiple videos on YouTube and want to check with you guys if my understanding is correct. I attach a small PDF presentation that I quickly made that goes through all the process steps, on how to get a transistor onto a bare wafer. Could you please check if the process flow and therefore my understanding is correct?

Am I understanding it correctly, that a "deposition process" is basically process step 8) and 14) from my PDF? In step 8, how does the "gaps" of the oxide layer get filled up?

Is step number 7 from my PDF what people refer to as doping? Is this the only time doping is necessary? How is this done? Is this basically "liquid n-doped Silicon" that is put there? And how is it put there?

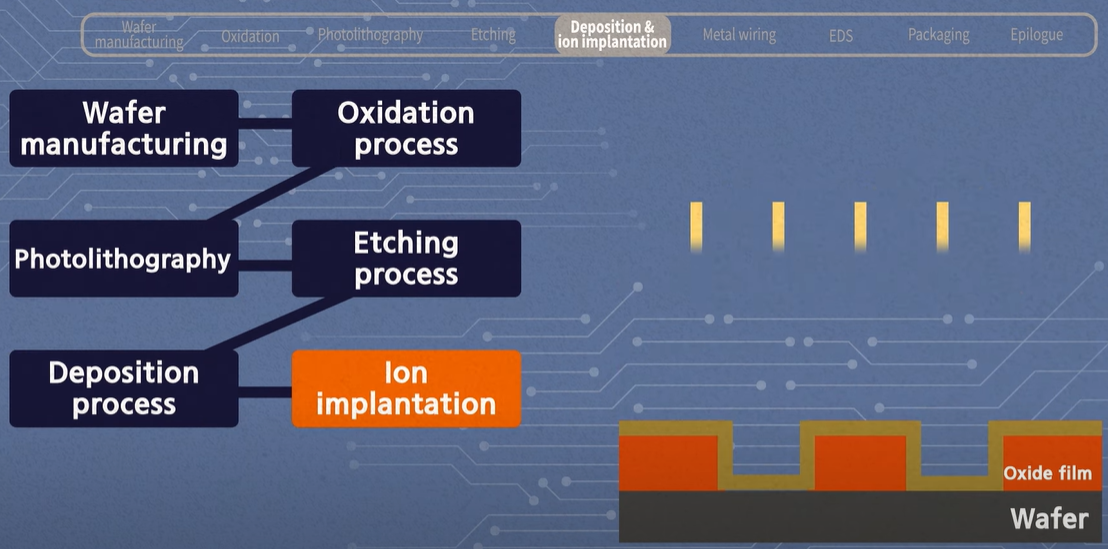

I saw on YT a video from Samsung, explaining the process:

In this picture, they show that the ion implantation comes after the deposition process? Isn`t this wrong? In this case the n-doped area of Silicon would be above the metal layer? This makes no sense to me? Besides this, in the schematics bottom right, there do not show the p- and n-type area in the wafer.

I hope someone can help me understanding this.

Thanks,

Tobias

I am currently diving deeper into the front-end of semiconductor processing and checking multiple sources to learn how it works. I came across multiple videos on YouTube and want to check with you guys if my understanding is correct. I attach a small PDF presentation that I quickly made that goes through all the process steps, on how to get a transistor onto a bare wafer. Could you please check if the process flow and therefore my understanding is correct?

Am I understanding it correctly, that a "deposition process" is basically process step 8) and 14) from my PDF? In step 8, how does the "gaps" of the oxide layer get filled up?

Is step number 7 from my PDF what people refer to as doping? Is this the only time doping is necessary? How is this done? Is this basically "liquid n-doped Silicon" that is put there? And how is it put there?

I saw on YT a video from Samsung, explaining the process:

In this picture, they show that the ion implantation comes after the deposition process? Isn`t this wrong? In this case the n-doped area of Silicon would be above the metal layer? This makes no sense to me? Besides this, in the schematics bottom right, there do not show the p- and n-type area in the wafer.

I hope someone can help me understanding this.

Thanks,

Tobias