When technology advances, complexities increase and data size becomes unmanageable. Fresh thinking and a new environment for automation are needed to provide the required increase in productivity. Specifically in case of circuit simulation of advanced-node analog designs, where precision is paramount and a large number of simulations must be performed over multiple corners under different modes of operation and testbenches, one cannot rely on manual management through legacy scripts. Of course a designer’s expertise is most important in the case of analog design, but circuit simulation of these designs requires an intuitive, intelligent and automated environment for analysis of the huge simulation results to boost productivity.

Having worked in custom design environment in my previous job, I have seen how native environments make simulators more powerful. It’s the environment that provides a complete solution and is the differentiator against point tools. An individual simulator can be integrated into design flows and managed through scripts, but that approach limits the scope for management and control of regressions; moreover the full potential of the simulator can seldom be exploited.

A simulator integrated in a 3[SUP]rd[/SUP] party design environment gets tied-up in that environment and there is often a lag in gaining access to its new features and capabilities; this problem was evident during my talk with Geoffrey Ying, Product Marketing Director for AMS group at Synopsys. On February 3, Synopsysannounced a brand new native environment that will be included at no additional cost with its circuit simulators. It seems to be a very powerful simulation environment; I personally liked some of the features that cater to key requirements of the analog design community today.

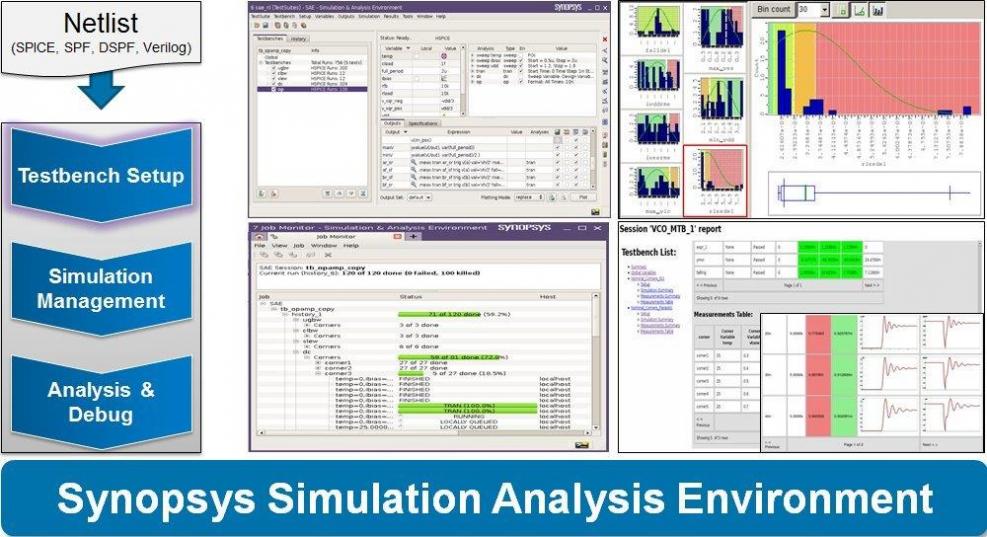

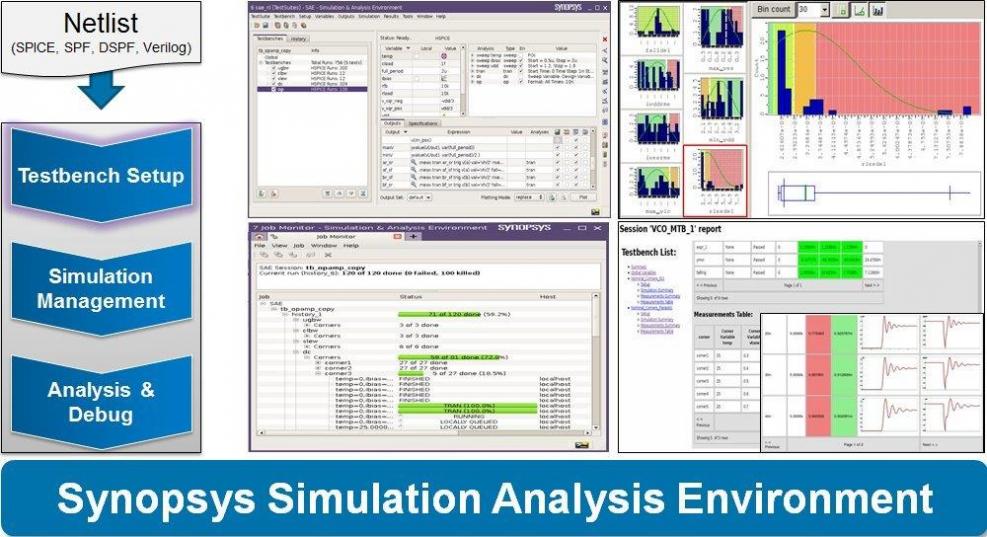

SynopsysSimulation Analysis Environment (SAE) will be integrated with HSPICE, FineSim SPICE and CustomSim in the 2016.03 release with the latest advanced simulation features available in the GUI environment. The highest level of precision for 16/10nm FinFET, as well as performance up to the giga-scale level can be obtained in the same environment by utilizing different simulators. The environment is easily customizable, and long simulation jobs can be distributed across a network.

A netlist read directly into the environment, intelligently parsed and understood in the right context provides a unique capability for analog and mixed-signal simulation setup where the netlist can be cross-probed with a visual representation of different simulation blocks under different directives. Testbenches, analysis types, design parameters, output measurement statements, and various other simulation setups can be done with ease. TCL scripts generated from interactive sessions can be customized further for regression runs in batch mode.

The SAE can directly read-in data from the design netlists, and analog/digital partitions can be easily visualized in the language-sensitive text editor or schematic of a mixed-signal design. Annotation for interface elements can be added in the schematic as well as text view. There are interesting simulation management features to assist comprehensive sweeps, corners and Monte Carlo simulation. An intuitive color scheme has been used to distinguish between min and max or pass and fail with ease. Multiple testbenches are supported with a history of results preserved for each testbench. Active job monitoring can be done where a long running job can be halted to let other high priority jobs precede for better resource management.

The SAE provides a powerful post simulation analysis and debugging environment where results are visible along with dynamic data filtering for pass/fail/all and their visual indicators as soon as they become available after the simulation run. The current results can be easily compared with historical results available in the system. The SAE also provides tight integration with Custom WaveViewfor debugging with actual waveforms.

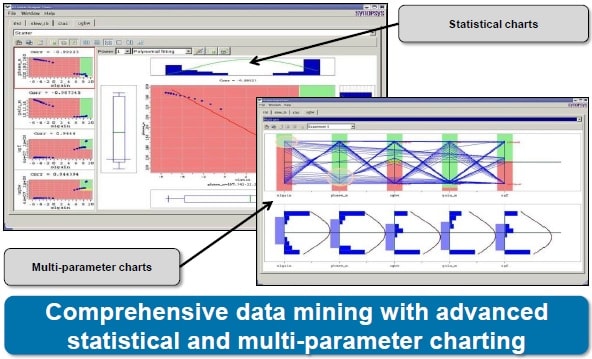

The Synopsys SAE provides a unique and powerful data mining and charting capability for root cause and correlation analysis. Statistical and multi-parameter charts are presented which provide direction to find the best set of desired parameters. The reports are web-based with hyperlinks in the testbenches that can be used for quick access to their corresponding results. The results can be navigated to analyze detailed measurement data and also to view the waveforms saved during simulation, that’s a unique feature.

Synopsys has disclosed in their press release that Samsung has deployed this new simulation environment in their System LSI business unit. Samsung’s System LSI BU was an early collaborator with Synopsys for conceptualizing this new environment; that’s like a customer-driven initiative.

The Synopsys SAE will be included with existing Synopsys simulators in their 2016.03 release in March of 2016 without any additional cost. This is a step in the right direction towards promotion of increased analog automation. Analog automation cannot be like digital, however intelligent, assisted tools and environments like these can increase productivity and throughput significantly for analog designs.

I guess most of the analog design community is familiar and has worked with Cadence ADE which has been around for a long time. Now Synopsys SAEis available for all analog and AMS designers using Synopsys simulators. Going forward, it is expected to interoperate with other simulators, as well.

The Synopsys press release is HERE.

Here is the link to register for the SAE webinar: Improving Analog Verification Productivity Using Synopsys Simulation and Analysis Environment (SAE)

Pawan Kumar Fangaria

Founder & President at www.fangarias.com

Comments

There are no comments yet.

You must register or log in to view/post comments.