Looking at a typical SoC design today it’s likely to contain a massive amount of memory IP, like: RAM, ROM, register files. Keeping memory close to the CPU makes sense for the lowest latency and highest performance metrics, but what about process variations affecting the memory operation? At the recent DAC conference held… Read More

Tag: customsim

Circuit Simulation Panel Discussion at #53DAC

Four panelists from big-name semiconductor design companies spoke about their circuit simulation experiences at #53DAC in Austin this year, so I attended to learn more about SPICE and Fast SPICE circuit simulation. I heard from the following four companies:… Read More

Synopsys’ New Circuit Simulation Environment Improves Productivity — for Free

When technology advances, complexities increase and data size becomes unmanageable. Fresh thinking and a new environment for automation are needed to provide the required increase in productivity. Specifically in case of circuit simulation of advanced-node analog designs, where precision is paramount and a large number… Read More

Circuit Simulation Update from #52DAC

Actual users of circuit simulators told their design and simulation stories at DAC during a luncheon sponsored by Synopsys on June 8th. I always prefer to hear from a design engineer versus a marketing person about what tool they use for circuit simulation, and how it helps them analyze their design goals. This year there were engineers… Read More

Bijan Kiani Talks Synopsys Custom Layout and More

Last week I sat down and talked to Bijan Kiani of Synopsys. He has marketing responsibility for design implementation products at Synopsys spanning digital, custom and analog mixed signal (AMS).

He was born in Iran and after high school he moved to the UK. He got his PhD degree from University of Edinburgh. It turns out that I was doing… Read More

Design & EDA Collaboration Advances Mixed-Signal Verification through VCS AMS

Last week it was a rare opportunity for me to attend a webinar where an SoC design house, a leading IP provider and a leading EDA tool provider joined together to present on how the tool capabilities are being used for advanced mixed-signal simulation of large designs, faster with accuracy. It’s always been a struggle to combine design… Read More

AMS Verification and Regression Testing of SoC Designs

Digital verification engineers on SoC designs have adopted many techniques to help ensure first silicon success: using compiled simulators, constrained random test, simulation farms, SystemVerilog methodology, and self-checking testbenches. AMS verification has tended to be ad-hoc or sharply divided into separate analog… Read More

AMS IC Simulation Update from Synopsys at DAC

Last year at DAC we didn’t really know the circuit simulation roadmap for Synopsys because of all the EDA company acquisitions, however this year it’s clear to me that:

- HSPICE continues on, although it’s a lower performance circuit simulator than FineSim

- FineSim from Magma is well-loved, and faster than HSPICE

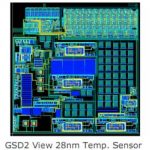

Analog IP Design at Moortec

Stephen Crosher started up Moortec in the UK back in 2005 with the help of his former Zarlink co-workers and they set to work offering AMS design services and eventually created their own Analog IP like the temperature sensor shown below:

We spoke by phone last week about his start-up experience and how they approach AMS design.… Read More