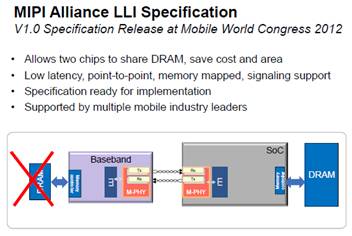

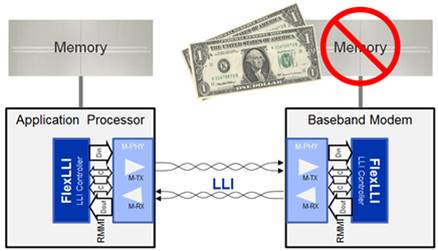

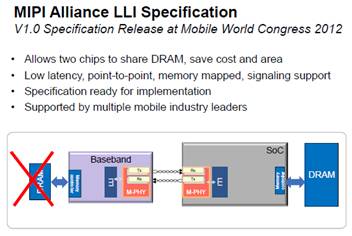

LLI Specification has been officially released by the MIPI Alliance, at the occasion of the Mobile World Congress in Barcelona, this year. As indicated by the name, the round-trip latency of the LLI inter-chip connection is fast enough for a mobile phone modem to share an application processor’s memory while maintaining enough read throughput and low latency for cache refills. Sharing the same DRAM device means the wireless handset integrator can save real estate printed circuit board (PCB) space and create a thinner smartphone, or implement additional device, more features to the smartphone, like NFC chip for example. It also means that the OEM will save, on every manufactured smartphone, the cost of one DRAM ($1 to 2$). If you manufacture dozen of million smartphone like some of the leaders, you can see how quickly you will get the return on the initial investment done by the chip makers to acquire the IP!

MIPI Alliance is strongly supportive of LLI, as we can see from this quote: “As active MIPI contributors, Synopsys and Arteris are aiding in the adoption of the MIPI M-PHY and MIPI Low Latency Interface,” said Joel Huloux, chairman of the board of MIPI Alliance. “The early integration and availability of the Arteris and Synopsys solution helps speed time to market for MIPI LLI adopters.” LLI support from Arteris and Synopsys illustrate how important is to build a strong partnership when selling a complementary solution, as the joint solution consists of Arteris’ Flex LLI™ MIPI LLI digital controller IP and Synopsys’ DesignWare® MIPI M-PHY IP. A team of Arteris and Synopsys engineers, formed to facilitate verification and testing of the joint solution, validated its functionality and interoperability. And for those who love to get insights, you should know that LLI was initially developed by an Application Processor chip maker, who understood that the function, to be successful on the market, has to be marketed and sold by an IP vendor, Arteris was selected as they were already marketing C2C or “Chip To Chip Link” IP, offering exactly the same functionality (sharing a DRAM between Modem and Application Processor), by the means of a parallel Interface, we will come back soon about this IP.

You will certainly get more information by registering and attend this webinar, just go here

Overview of this webinar:

When designing mobile devices, it is critical to implement technologies that will future-proof your design, minimize BOM costs and board space, and maintain or improve performance. The MIPI Alliance Low Latency Interface (LLI) and M-PHY are two technologies that can help future-proof your design while giving it competitive advantages in terms of cost, board space, performance, and time-to-market.

The webinar will present a case study describing how LLI can be used to minimize DRAM footprint on a mobile phone system board. Particular attention will be paid to real-world implementation issues, such as clock domain, power and voltage management as well as integration with SoC interconnect fabrics.

This webinar will teach you:

- What the LLI and M-PHY technologies are, and best practices for implementation

- How LLI is different than other chip-to-chip interface standards, such as USB and PCIe

- How the LLI point-to-point interconnect can benefit multi-chip systems

- How the LLI controller and M-PHY IP can reduce the silicon footprint on your board

- How LLI can reduce individual BOM and multi-product platform costs

Who should attend:

This webinar is targeted at system architects, mobile device and consumer electronics product managers and designers, design engineers, SoC architects, and project managers.

Presenters:

Hezi Saar, Staff Product Marketing Manager, Synopsys

Hezi Saar serves as a staff product marketing manager at Synopsys and is responsible for its DesignWare MIPI controller and PHY IP product line. He brings more than 17 years of experience in the semiconductor and electronics industries in embedded systems. Prior to joining Synopsys, from 2004 to 2009, Saar served as senior product marketing manager leading Actel’s Flash field-programmable-gate-array (FPGA) product lines. Previously, he served as a product marketing manager at ISD/Winbond and as a senior design engineer at RAD Data Communications. Saar holds a bachelor of science degree from Tel Aviv University in computer science and economics and an MBA from Columbia Southern University.

Kurt Shuler, VP of Marketing, Arteris

Kurt Shuler is the VP of marketing at Arteris. He has held senior roles at Intel, Texas Instruments, ARC International and two startups, Virtio and Tenison. Before working in high technology, Kurt flew as an air commando in the U.S. Air Force Special Operations Forces. Kurt earned a B.S. in Aeronautical Engineering from the U.S. Air Force Academy and an MBA from the MIT Sloan School of Management.

Philippe Martin, Vice President, Corporate Applications and Senior Fellow, Arteris

Philippe Martin is Vice President, Corporate Applications and Senior Fellow at Arteris. He has been involved in the development of the MIPI Alliance Low Latency Interface (LLI) specification since the creation of the MIPI Alliance LLI Investigation Group in 2009. Philippe is a renowned expert on LLI and has contributed to the technology through the MIPI Alliance LLI Working Group. Philippe has also participated in the first two commercial implementations by semiconductor companies of the LLI standard.

By Eric EstevefromIPNEST

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.