Engineers love to optimize their designs, but that implies that there are models and stimulus to automate the process. Process engineers have TCAD tools, circuit designers have SPICE for circuit simulation, logic designers have gate-level simulators, RTL designers use logic simulation, but what is there for the system architects of a processor or SoC design? Even back in the 1980s at Intel, I recall that the architect coded a GPU architecture in the MainSail language and then pushed some stimulus through it to find out what the performance and bottle-necks would be, all prior to any detailed implementation, but that was a lot of error-prone, hand-coding required.

In 2021 there’s a system engineering company called Mirabilis Design, and they have focused on providing a system architect with a modeling and analysis environment to do actual exploration, and make the trade-offs to pick the winning architecture. I spoke with the founder of Mirabilis Design, Deepak Shankar to learn about his upcoming webinar.

Webinar

System architects have high-level questions that need to be answered, like: how will my SoC respond to network traffic, what is the Quality Of Service (QOS), and how should the Network On Chip (NOC) be configured?

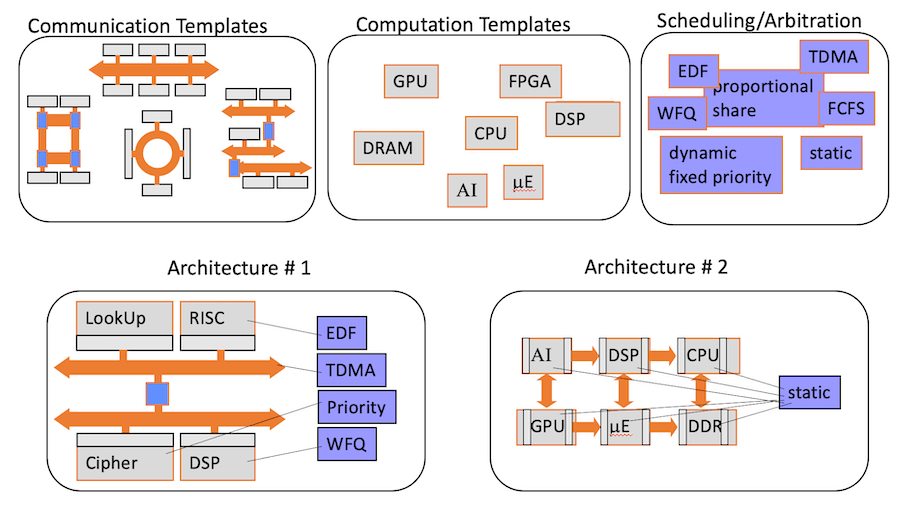

I learned that the approach from Mirabilis is to use a system-level simulator, along with a library of 500 models for things like: queuing, networking, ARM M1, RISC V, etc. Most of these models are parameterized, like a scheduler, so you can get the proper configuration. If you wanted a system to have an Arteris NOC, ARM M1 core and use LPDDR5 interface to RAM, then how would they all work together, and how should the NOC be setup?

If the block that you want isn’t already modeled in the library, then there’s a way for you to quickly build your own, or even modify the source code of an existing library block.

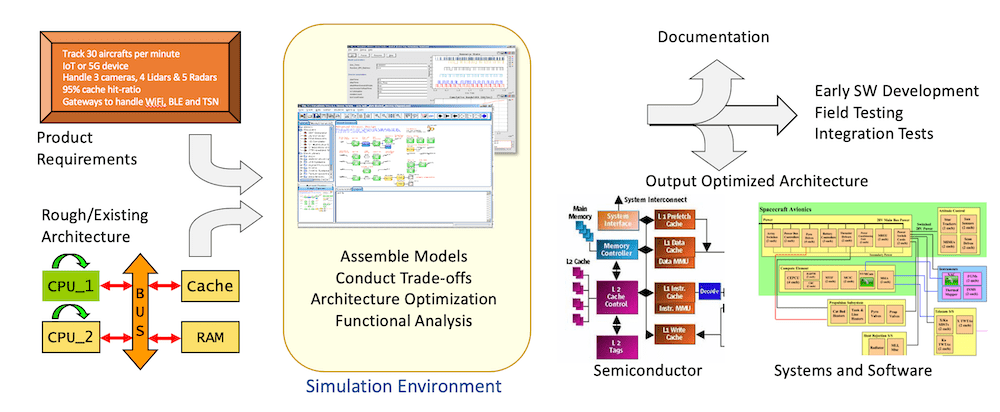

In the webinar you’ll get to see two cases where The VisualSim environment is used to evaluate the requirements, power, performance and function of a Processor and an SoC design. The architectural exploration flow with this approach looks like this:

What struck me most with Mirabilis was that architects can now get early access to throughput, performance, power and even timing, all before detailed implementation is started. Power estimation and performance modeling are no longer split between two different groups of engineers, with two different sets of tools.

Results from VisualSim on the power estimation side are typically within 5-7% of what you’ll measure in silicon, and that’s quite valuable, because other approaches are lucky to be within 50% of silicon values.

Mark your calendar for May 27th, from 10AM to 11AM PDT, then sign up online for this informative webinar from Mirabilis Design.

Mirabilis

Mirabilis Design provides modeling, exploration and collaboration solutions for semiconductors, digital electronics and Embedded Systems. Clientele includes a mix of semiconductor, defense, aerospace, automotive and computing product suppliers. 6 of the top 12 semiconductor companies, 8 of the top 15 defense suppliers and 4 of the top 10 electronics companies use VisualSim to ensure the right design for their products.

Also Read:

WEBINAR: Balancing Performance and Power in adding AI Accelerators to System-on-Chip (SoC)

Webinar – Comparing ARM and RISC-V Cores

System-Level Modeling using your Web Browser

Share this post via:

Facing the Quantum Nature of EUV Lithography