The EDA tools industry relies upon ongoing productivity enhancements to existing products, to manage increasing SoC complexity and to address shrinking design schedules. The source of ideas for enhancements can come from a variety of sources – e.g., customer feedback, collaboration with the foundries, and features found in tools used by other domains (package and/or PCB design).

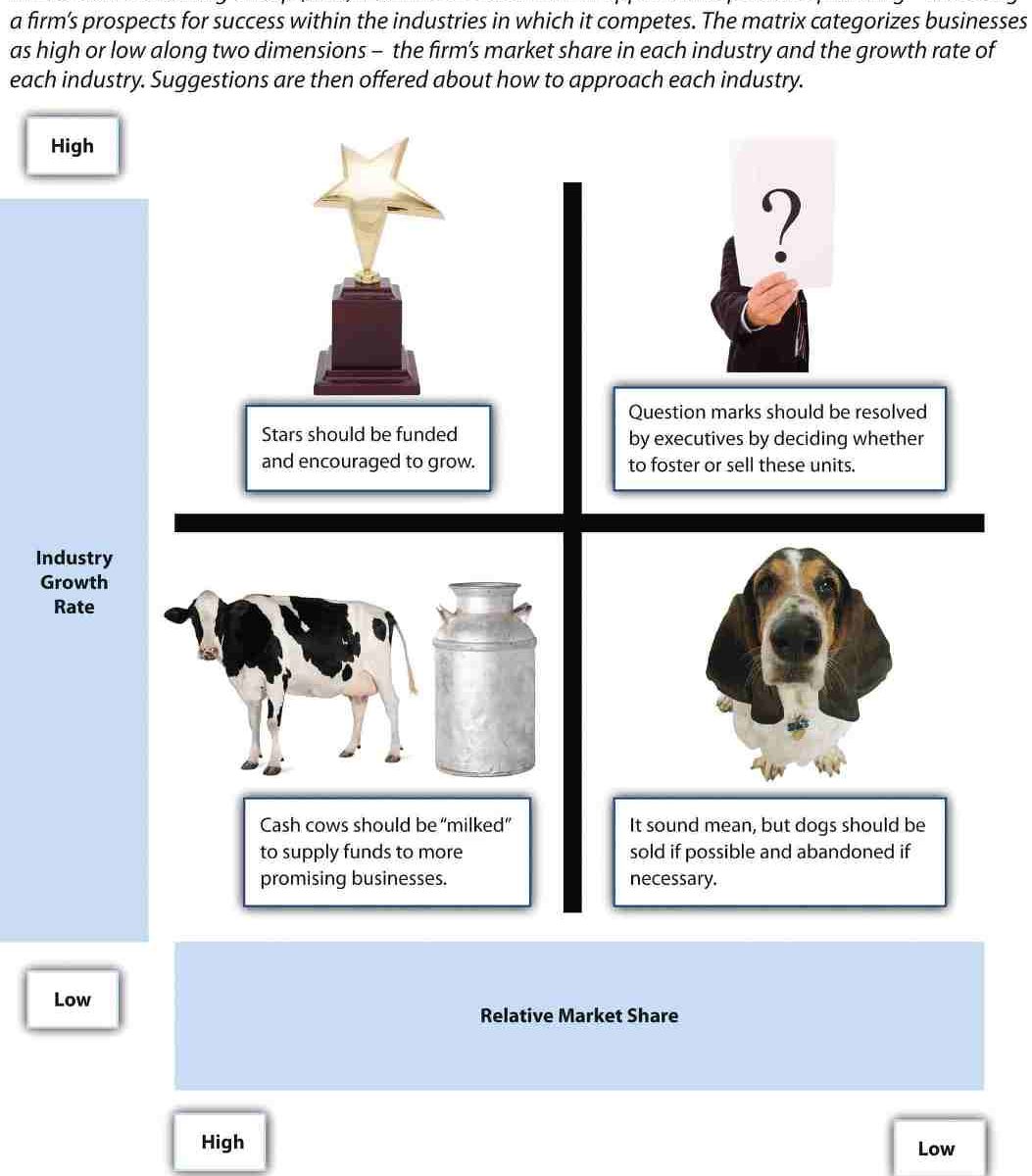

A prevalent economic theory, known as the BCG model, categorizes products into four sets – stars; cash cows; question marks; and dogs. The theory is supposed to guide companies on how to invest free cash flow on product R&D. Cash cows are high market share products that have a low growth rate, that provide funding for potential stars (and question marks). This model may be fine for Kellogg’s Corn Flakes, Coca-Cola, Ford pickup trucks, and even software products like Microsoft Office, but is definitely not applicable to the EDA tools that are fundamental to SoC designs.

A case in point is the market share-leading Virtuoso Layout Suite (VLS) from Cadence. The VLS product family has been the predominant physical layout platform for custom digital, analog, and RF design for decades. The platform has remained the market leader due to the continued focus on improving designer productivity – this is once again demonstrated by the recent announcement of key VLS enhancements.

Parenthetically, please note that a couple of years ago, Cadence split the VLS product family into two code streams – the release 6.x (e.g., v6.1.7) and the release 12.x (e.g., v12.2) products. The base productivity enhancements are incorporated into both releases, while specific additional capabilities required by new process nodes are only added to the Virtuoso Advanced Node (12.x) platform.

I recently had the opportunity to chat with Mike Kelly, Director, Virtuoso Product Marketing, about some of the productivity features recently added.

(There are new capabilities being developed by Cadence in 12.x specifically for the requirements of 10nm and 7nm process nodes, as well – look for a subsequent semiwiki article to review some of the new functionality.)

Mike highlighted that among the existing VLS 6.x family customers, there are lots of new design starts in process nodes from 180nm to 28nm, in support of the growing applications areas of automotive, RF, and IoT. And, there are emerging markets which bring unique requirements to existing physical layout design, such as silicon photonics (link).

One of the key considerations in EDA tool development is the compatibility of existing datasets with new releases. Mike confirmed that these productivity enhancements use the same Virtuoso libraries and views – there are no project design migration issues.

Graphic Rendering Enhancements

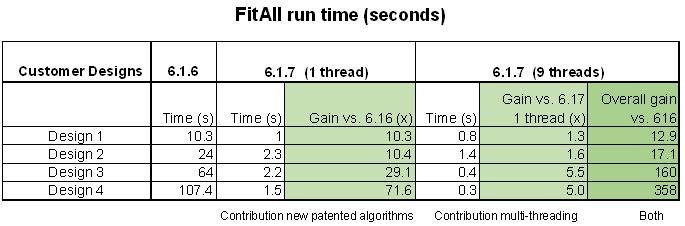

Mike indicated, “We responded to customer feedback, who wanted faster performance for common layout tasks, especially on large datasets. We’ve implemented new rendering algorithms, and also added multithreading support. Fit, pan, zoom, drag, and redraw operations are vastly improved, by 10X to over 100X.”

This improved performance applies not only to initial layout design, but also extends to the debug phase, where designers are cross-referencing to the DRC and LVS results from Cadence’s Physical Verification System (PVS).

Ruler Enhancements

Cadence also worked closely with customers to evaluate session log files, to see what commands are used most often, and would be candidates for performance profiling and enhancement. It’s likely no surprise that one of the most common operations in custom layout design is “zoom in, pop-up ruler, measure, zoom out”.

The latest 6.1.7 and 12.2 releases include a dynamic measurement feature, where user setup enables interactive layer/shape measurement, replacing the current ruler command sequence.

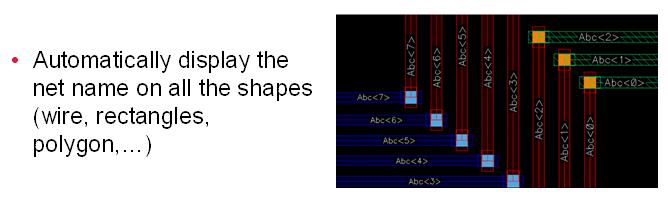

Dynamic Net Labeling

As mentioned above, sometimes great ideas for new EDA tool features come from other technology sources. Mike offered this example. “One of the key features of the Cadence Allegro PCB tool annotates signal nets with their name during interactive editing. Leveraging the custom schematic-driven layout connectivity model within Virtuoso, we added dynamic net labeling in VLS, as well.”

ModGen updates

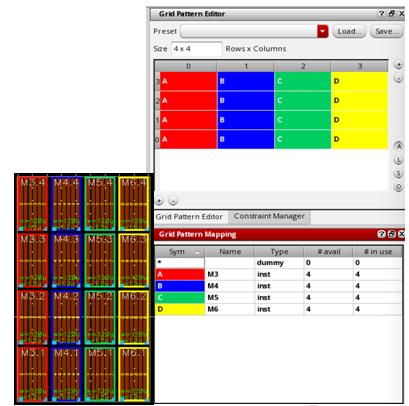

Perhaps the most significant enhancements to VLS pertain to the accelerated methodology for creating complex block layouts, combining new features of the Module Generator (ModGen) and the device-level Space-Based Router technologies.

ModGen now supports a pattern mapping input description methodology, using the Graphic Pattern Editor. Designers can now more easily describe the placement of arrays of pCells, readily supporting the unique centroid patterns required for analog circuit matching, to reduce the impact of local process variation. (pCells support all the requisite features for layout optimization, such as common source/drain node merging.)

The automated (and interactive) space-based routing technology integrated within ModGen offers a rich set of routing topologies and options – e.g., point-to-point, trunk-to-pin, cloning.

Clearly, the EDA industry must follow a unique product development business model, where a constant focus on user productivity is required. An example of that focus is demonstrated in the recent set of enhancements in Cadence’s Virtuoso Layout Suite. In the business lingo of the BCG matrix, it remains “a star”.

This article could only cover some of the recent VLS enhancements – for more details, please follow this link.

-chipguy

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.